| META FILEATTACHMENT |

attachment="OFTC_0.pdf" attr="" comment="" date="1495691002" name="OFTC_0.pdf" path="OFTC_0.pdf" size="619576" user="AtlasjSilicon" version="1" |

| META FILEATTACHMENT |

attachment="OFTC_1.pdf" attr="" comment="" date="1495691074" name="OFTC_1.pdf" path="OFTC_1.pdf" size="1782077" user="AtlasjSilicon" version="1" |

| META FILEATTACHMENT |

attachment="OFTC_2_1.pdf" attr="" comment="" date="1495691072" name="OFTC_2_1.pdf" path="OFTC_2_1.pdf" size="715575" user="AtlasjSilicon" version="1" |

| META FILEATTACHMENT |

attachment="OFTC_2_2.pdf" attr="" comment="" date="1495691071" name="OFTC_2_2.pdf" path="OFTC_2_2.pdf" size="2444807" user="AtlasjSilicon" version="1" |

| META FILEATTACHMENT |

attachment="OFTC_2_3.pdf" attr="" comment="" date="1495691069" name="OFTC_2_3.pdf" path="OFTC_2_3.pdf" size="2034260" user="AtlasjSilicon" version="1" |

| META FILEATTACHMENT |

attachment="OFTC_2_4.pdf" attr="" comment="" date="1495691067" name="OFTC_2_4.pdf" path="OFTC_2_4.pdf" size="4361927" user="AtlasjSilicon" version="1" |

| META FILEATTACHMENT |

attachment="OFTC_3.pdf" attr="" comment="" date="1495691064" name="OFTC_3.pdf" path="OFTC_3.pdf" size="734423" user="AtlasjSilicon" version="1" |

| META FILEATTACHMENT |

attachment="OFTC_4_1.pdf" attr="" comment="" date="1495691063" name="OFTC_4_1.pdf" path="OFTC_4_1.pdf" size="459407" user="AtlasjSilicon" version="1" |

| META FILEATTACHMENT |

attachment="OFTC_4_2.pdf" attr="" comment="" date="1495691062" name="OFTC_4_2.pdf" path="OFTC_4_2.pdf" size="2509991" user="AtlasjSilicon" version="1" |

| META FILEATTACHMENT |

attachment="OFTC_4_3.pdf" attr="" comment="" date="1495691059" name="OFTC_4_3.pdf" path="OFTC_4_3.pdf" size="2868757" user="AtlasjSilicon" version="1" |

| META FILEATTACHMENT |

attachment="OFTC_5.pdf" attr="" comment="" date="1495691157" name="OFTC_5.pdf" path="OFTC_5.pdf" size="394077" user="AtlasjSilicon" version="1" |

| META FILEATTACHMENT |

attachment="OFTC_6.pdf" attr="" comment="" date="1495691157" name="OFTC_6.pdf" path="OFTC_6.pdf" size="1379534" user="AtlasjSilicon" version="1" |

| META FILEATTACHMENT |

attachment="OFTC_7.pdf" attr="" comment="" date="1495691155" name="OFTC_7.pdf" path="OFTC_7.pdf" size="3203127" user="AtlasjSilicon" version="1" |

| META FILEATTACHMENT |

attachment="OFTC_8.pdf" attr="" comment="" date="1495691149" name="OFTC_8.pdf" path="OFTC_8.pdf" size="712487" user="AtlasjSilicon" version="1" |

| META FILEATTACHMENT |

attachment="OFTC_9.pdf" attr="" comment="" date="1495691149" name="OFTC_9.pdf" path="OFTC_9.pdf" size="1473549" user="AtlasjSilicon" version="1" |

| META FILEATTACHMENT |

attachment="OFTC_lab_c1_rev20.pdf" attr="" comment="" date="1495691146" name="OFTC_lab_c1_rev20.pdf" path="OFTC_lab_c1_rev20.pdf" size="125624" user="AtlasjSilicon" version="1" |

| META FILEATTACHMENT |

attachment="OFTC_lab_i1_rev11.pdf" attr="" comment="" date="1495691146" name="OFTC_lab_i1_rev11.pdf" path="OFTC_lab_i1_rev11.pdf" size="108370" user="AtlasjSilicon" version="1" |

| META FILEATTACHMENT |

attachment="OFTC_lab_i2_rev13.pdf" attr="" comment="" date="1495691146" name="OFTC_lab_i2_rev13.pdf" path="OFTC_lab_i2_rev13.pdf" size="107314" user="AtlasjSilicon" version="1" |

| META FILEATTACHMENT |

attachment="OFTC_lab_s1_rev20.pdf" attr="" comment="" date="1495691146" name="OFTC_lab_s1_rev20.pdf" path="OFTC_lab_s1_rev20.pdf" size="134142" user="AtlasjSilicon" version="1" |

| META FILEATTACHMENT |

attachment="OFTC_preparation.pdf" attr="" comment="" date="1495691197" name="OFTC_preparation.pdf" path="OFTC_preparation.pdf" size="2066566" user="AtlasjSilicon" version="1" |

| META FILEATTACHMENT |

attachment="OFTC_ref_note.pdf" attr="" comment="" date="1495691192" name="OFTC_ref_note.pdf" path="OFTC_ref_note.pdf" size="48837" user="AtlasjSilicon" version="1" |

| META FILEATTACHMENT |

attachment="references.pdf" attr="" comment="" date="1495693148" name="references.pdf" path="references.pdf" size="892748" user="AtlasjSilicon" version="1" |

| META FILEATTACHMENT |

attachment="LVDS2SLVS_Pins.zip" attr="" comment="" date="1495793797" name="LVDS2SLVS_Pins.zip" path="LVDS2SLVS_Pins.zip" size="217304" user="AtlasjSilicon" version="1" |

| META FILEATTACHMENT |

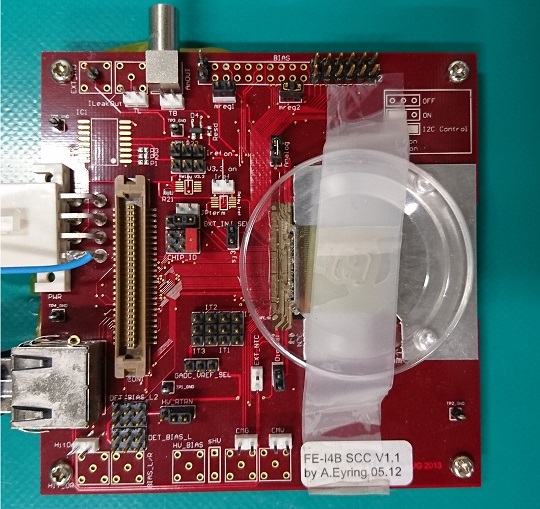

attachment="FEI4BSCC.jpg" attr="h" comment="" date="1498471156" name="FEI4BSCC.jpg" path="FEI4BSCC.jpg" size="136127" user="AtlasjSilicon" version="1" |

| META FILEATTACHMENT |

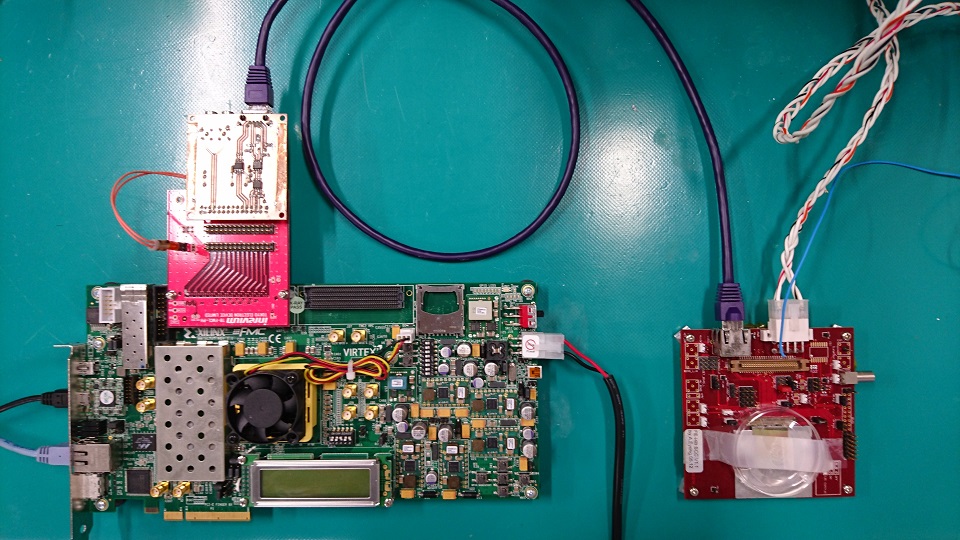

attachment="VC707_setup.jpg" attr="h" comment="" date="1498471264" name="VC707_setup.jpg" path="VC707_setup.jpg" size="225804" user="AtlasjSilicon" version="1" |