Difference: RD53ADAQdevelopment (1 vs. 25)

Revision 252018-02-09 - KojiNakamura

RD53A DAQ Development | |||||||||||||||||||||||||||||||||||||||||||||||||||

| Added: | |||||||||||||||||||||||||||||||||||||||||||||||||||

| > > | |||||||||||||||||||||||||||||||||||||||||||||||||||

IntroductionRD53 is a prospective ASIC for the HL-LHC upgrade. | |||||||||||||||||||||||||||||||||||||||||||||||||||

| Deleted: | |||||||||||||||||||||||||||||||||||||||||||||||||||

| < < | |||||||||||||||||||||||||||||||||||||||||||||||||||

/opt/Xilinx/Vivado/2016.4/data/xicom/cable_drivers/lin64/install_script/install_drivers sudo ./install_drivers | |||||||||||||||||||||||||||||||||||||||||||||||||||

| Deleted: | |||||||||||||||||||||||||||||||||||||||||||||||||||

| < < | -- | ||||||||||||||||||||||||||||||||||||||||||||||||||

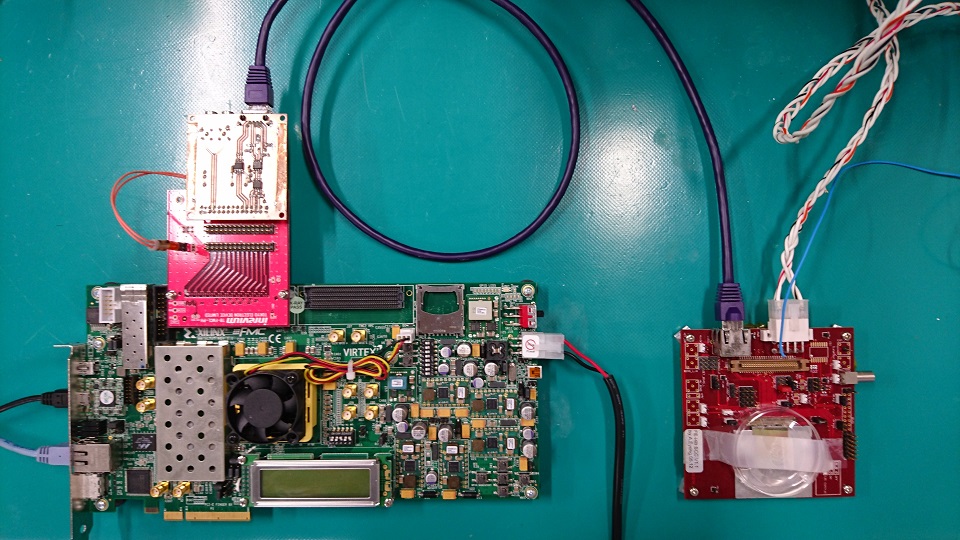

FE-I4 Readout Test* Gitlab repository

YARR

Tips

| |||||||||||||||||||||||||||||||||||||||||||||||||||

| Changed: | |||||||||||||||||||||||||||||||||||||||||||||||||||

| < < | Comments | ||||||||||||||||||||||||||||||||||||||||||||||||||

| > > | RD53A probe card | ||||||||||||||||||||||||||||||||||||||||||||||||||

| Changed: | |||||||||||||||||||||||||||||||||||||||||||||||||||

| < < | |||||||||||||||||||||||||||||||||||||||||||||||||||

| > > | RD53AProbeCard | ||||||||||||||||||||||||||||||||||||||||||||||||||

| Added: | |||||||||||||||||||||||||||||||||||||||||||||||||||

| > > |

-- | ||||||||||||||||||||||||||||||||||||||||||||||||||

| |||||||||||||||||||||||||||||||||||||||||||||||||||

Revision 242017-08-18 - AtlasjSilicon

RD53A DAQ DevelopmentIntroductionRD53 is a prospective ASIC for the HL-LHC upgrade./opt/Xilinx/Vivado/2016.4/data/xicom/cable_drivers/lin64/install_script/install_drivers sudo ./install_drivers-- FE-I4 Readout Test | |||||||||||||||||||||||||||||||||||||||||||||||||||

| Changed: | |||||||||||||||||||||||||||||||||||||||||||||||||||

| < < | Git | ||||||||||||||||||||||||||||||||||||||||||||||||||

| > > | * Gitlab repository | ||||||||||||||||||||||||||||||||||||||||||||||||||

| |||||||||||||||||||||||||||||||||||||||||||||||||||

| Changed: | |||||||||||||||||||||||||||||||||||||||||||||||||||

| < < |

| ||||||||||||||||||||||||||||||||||||||||||||||||||

| > > |

| ||||||||||||||||||||||||||||||||||||||||||||||||||

| |||||||||||||||||||||||||||||||||||||||||||||||||||

| Changed: | |||||||||||||||||||||||||||||||||||||||||||||||||||

| < < |

| ||||||||||||||||||||||||||||||||||||||||||||||||||

| > > |

| ||||||||||||||||||||||||||||||||||||||||||||||||||

| Deleted: | |||||||||||||||||||||||||||||||||||||||||||||||||||

| < < |

| ||||||||||||||||||||||||||||||||||||||||||||||||||

YARR

Tips

Comments

| |||||||||||||||||||||||||||||||||||||||||||||||||||

Revision 232017-08-03 - AtlasjSilicon

RD53A DAQ DevelopmentIntroductionRD53 is a prospective ASIC for the HL-LHC upgrade. | |||||||||||||||||||||||||||||||||||||||||||||||||||

| Added: | |||||||||||||||||||||||||||||||||||||||||||||||||||

| > > | |||||||||||||||||||||||||||||||||||||||||||||||||||

/opt/Xilinx/Vivado/2016.4/data/xicom/cable_drivers/lin64/install_script/install_drivers sudo ./install_drivers-- FE-I4 Readout Test | |||||||||||||||||||||||||||||||||||||||||||||||||||

| Added: | |||||||||||||||||||||||||||||||||||||||||||||||||||

| > > |

Git | ||||||||||||||||||||||||||||||||||||||||||||||||||

| |||||||||||||||||||||||||||||||||||||||||||||||||||

| Changed: | |||||||||||||||||||||||||||||||||||||||||||||||||||

| < < |

| ||||||||||||||||||||||||||||||||||||||||||||||||||

| > > |

| ||||||||||||||||||||||||||||||||||||||||||||||||||

| |||||||||||||||||||||||||||||||||||||||||||||||||||

| Changed: | |||||||||||||||||||||||||||||||||||||||||||||||||||

| < < |

| ||||||||||||||||||||||||||||||||||||||||||||||||||

| > > |

| ||||||||||||||||||||||||||||||||||||||||||||||||||

| |||||||||||||||||||||||||||||||||||||||||||||||||||

| Deleted: | |||||||||||||||||||||||||||||||||||||||||||||||||||

| < < |

| ||||||||||||||||||||||||||||||||||||||||||||||||||

YARR

Tips

Comments

| |||||||||||||||||||||||||||||||||||||||||||||||||||

Revision 222017-07-26 - AtlasjSilicon

RD53A DAQ DevelopmentIntroductionRD53 is a prospective ASIC for the HL-LHC upgrade. | |||||||||||||||||||||||||||||||||||||||||||||||||||

| Deleted: | |||||||||||||||||||||||||||||||||||||||||||||||||||

| < < | |||||||||||||||||||||||||||||||||||||||||||||||||||

/opt/Xilinx/Vivado/2016.4/data/xicom/cable_drivers/lin64/install_script/install_drivers sudo ./install_drivers-- FE-I4 Readout Test

| |||||||||||||||||||||||||||||||||||||||||||||||||||

| Changed: | |||||||||||||||||||||||||||||||||||||||||||||||||||

| < < |

| ||||||||||||||||||||||||||||||||||||||||||||||||||

| > > |

| ||||||||||||||||||||||||||||||||||||||||||||||||||

YARR

Tips

Comments

| |||||||||||||||||||||||||||||||||||||||||||||||||||

Revision 212017-07-13 - AtlasjSilicon

RD53A DAQ DevelopmentIntroductionRD53 is a prospective ASIC for the HL-LHC upgrade./opt/Xilinx/Vivado/2016.4/data/xicom/cable_drivers/lin64/install_script/install_drivers sudo ./install_drivers-- FE-I4 Readout Test

| |||||||||||||||||||||||||||||||||||||||||||||||||||

| Added: | |||||||||||||||||||||||||||||||||||||||||||||||||||

| > > | YARR

| ||||||||||||||||||||||||||||||||||||||||||||||||||

Tips

Comments

| |||||||||||||||||||||||||||||||||||||||||||||||||||

Revision 202017-07-07 - AtlasjSilicon

RD53A DAQ DevelopmentIntroductionRD53 is a prospective ASIC for the HL-LHC upgrade./opt/Xilinx/Vivado/2016.4/data/xicom/cable_drivers/lin64/install_script/install_drivers sudo ./install_drivers-- FE-I4 Readout Test

| |||||||||||||||||||||||||||||||||||||||||||||||||||

| Changed: | |||||||||||||||||||||||||||||||||||||||||||||||||||

| < < |

| ||||||||||||||||||||||||||||||||||||||||||||||||||

| > > |

| ||||||||||||||||||||||||||||||||||||||||||||||||||

Tips

Comments

| |||||||||||||||||||||||||||||||||||||||||||||||||||

Revision 192017-06-29 - AtlasjSilicon

RD53A DAQ DevelopmentIntroductionRD53 is a prospective ASIC for the HL-LHC upgrade. | |||||||||||||||||||||||||||||||||||||||||||||||||||

| Added: | |||||||||||||||||||||||||||||||||||||||||||||||||||

| > > | |||||||||||||||||||||||||||||||||||||||||||||||||||

/opt/Xilinx/Vivado/2016.4/data/xicom/cable_drivers/lin64/install_script/install_drivers sudo ./install_drivers-- FE-I4 Readout Test

| |||||||||||||||||||||||||||||||||||||||||||||||||||

| Added: | |||||||||||||||||||||||||||||||||||||||||||||||||||

| > > | |||||||||||||||||||||||||||||||||||||||||||||||||||

Tips

Comments

| |||||||||||||||||||||||||||||||||||||||||||||||||||

Revision 182017-06-29 - AtlasjSilicon

RD53A DAQ DevelopmentIntroductionRD53 is a prospective ASIC for the HL-LHC upgrade./opt/Xilinx/Vivado/2016.4/data/xicom/cable_drivers/lin64/install_script/install_drivers sudo ./install_drivers-- FE-I4 Readout Test

| |||||||||||||||||||||||||||||||||||||||||||||||||||

| Added: | |||||||||||||||||||||||||||||||||||||||||||||||||||

| > > |

| ||||||||||||||||||||||||||||||||||||||||||||||||||

Tips

Comments

| |||||||||||||||||||||||||||||||||||||||||||||||||||

Revision 172017-06-28 - AtlasjSilicon

RD53A DAQ DevelopmentIntroductionRD53 is a prospective ASIC for the HL-LHC upgrade./opt/Xilinx/Vivado/2016.4/data/xicom/cable_drivers/lin64/install_script/install_drivers sudo ./install_drivers-- FE-I4 Readout Test

| |||||||||||||||||||||||||||||||||||||||||||||||||||

| Changed: | |||||||||||||||||||||||||||||||||||||||||||||||||||

| < < |

| ||||||||||||||||||||||||||||||||||||||||||||||||||

| > > |

| ||||||||||||||||||||||||||||||||||||||||||||||||||

| |||||||||||||||||||||||||||||||||||||||||||||||||||

| Changed: | |||||||||||||||||||||||||||||||||||||||||||||||||||

| < < |

| ||||||||||||||||||||||||||||||||||||||||||||||||||

| > > |

| ||||||||||||||||||||||||||||||||||||||||||||||||||

| |||||||||||||||||||||||||||||||||||||||||||||||||||

| Added: | |||||||||||||||||||||||||||||||||||||||||||||||||||

| > > |

| ||||||||||||||||||||||||||||||||||||||||||||||||||

| |||||||||||||||||||||||||||||||||||||||||||||||||||

| Changed: | |||||||||||||||||||||||||||||||||||||||||||||||||||

| < < |

| ||||||||||||||||||||||||||||||||||||||||||||||||||

| > > |

| ||||||||||||||||||||||||||||||||||||||||||||||||||

| Added: | |||||||||||||||||||||||||||||||||||||||||||||||||||

| > > |

| ||||||||||||||||||||||||||||||||||||||||||||||||||

| |||||||||||||||||||||||||||||||||||||||||||||||||||

| Deleted: | |||||||||||||||||||||||||||||||||||||||||||||||||||

| < < |

| ||||||||||||||||||||||||||||||||||||||||||||||||||

Tips

Comments

| |||||||||||||||||||||||||||||||||||||||||||||||||||

Revision 162017-06-28 - AtlasjSilicon

RD53A DAQ DevelopmentIntroductionRD53 is a prospective ASIC for the HL-LHC upgrade./opt/Xilinx/Vivado/2016.4/data/xicom/cable_drivers/lin64/install_script/install_drivers sudo ./install_drivers-- FE-I4 Readout Test

| |||||||||||||||||||||||||||||||||||||||||||||||||||

| Added: | |||||||||||||||||||||||||||||||||||||||||||||||||||

| > > |

| ||||||||||||||||||||||||||||||||||||||||||||||||||

Tips

Comments

| |||||||||||||||||||||||||||||||||||||||||||||||||||

Revision 152017-06-27 - AtlasjSilicon

RD53A DAQ DevelopmentIntroductionRD53 is a prospective ASIC for the HL-LHC upgrade./opt/Xilinx/Vivado/2016.4/data/xicom/cable_drivers/lin64/install_script/install_drivers sudo ./install_drivers-- FE-I4 Readout Test

| |||||||||||||||||||||||||||||||||||||||||||||||||||

| Changed: | |||||||||||||||||||||||||||||||||||||||||||||||||||

| < < |

| ||||||||||||||||||||||||||||||||||||||||||||||||||

| > > |

| ||||||||||||||||||||||||||||||||||||||||||||||||||

| Added: | |||||||||||||||||||||||||||||||||||||||||||||||||||

| > > |

| ||||||||||||||||||||||||||||||||||||||||||||||||||

| |||||||||||||||||||||||||||||||||||||||||||||||||||

| Added: | |||||||||||||||||||||||||||||||||||||||||||||||||||

| > > |

| ||||||||||||||||||||||||||||||||||||||||||||||||||

Tips

Comments

| |||||||||||||||||||||||||||||||||||||||||||||||||||

Revision 142017-06-27 - AtlasjSilicon

RD53A DAQ DevelopmentIntroductionRD53 is a prospective ASIC for the HL-LHC upgrade./opt/Xilinx/Vivado/2016.4/data/xicom/cable_drivers/lin64/install_script/install_drivers sudo ./install_drivers-- FE-I4 Readout Test

| |||||||||||||||||||||||||||||||||||||||||||||||||||

| Changed: | |||||||||||||||||||||||||||||||||||||||||||||||||||

| < < |

| ||||||||||||||||||||||||||||||||||||||||||||||||||

| > > |

| ||||||||||||||||||||||||||||||||||||||||||||||||||

| Added: | |||||||||||||||||||||||||||||||||||||||||||||||||||

| > > |

| ||||||||||||||||||||||||||||||||||||||||||||||||||

| |||||||||||||||||||||||||||||||||||||||||||||||||||

| Changed: | |||||||||||||||||||||||||||||||||||||||||||||||||||

| < < |

| ||||||||||||||||||||||||||||||||||||||||||||||||||

| > > |

| ||||||||||||||||||||||||||||||||||||||||||||||||||

Tips

Comments

| |||||||||||||||||||||||||||||||||||||||||||||||||||

Revision 132017-06-26 - AtlasjSilicon

RD53A DAQ DevelopmentIntroductionRD53 is a prospective ASIC for the HL-LHC upgrade. | |||||||||||||||||||||||||||||||||||||||||||||||

| Deleted: | |||||||||||||||||||||||||||||||||||||||||||||||

| < < | |||||||||||||||||||||||||||||||||||||||||||||||

/opt/Xilinx/Vivado/2016.4/data/xicom/cable_drivers/lin64/install_script/install_drivers sudo ./install_drivers-- FE-I4 Readout Test | |||||||||||||||||||||||||||||||||||||||||||||||

| Changed: | |||||||||||||||||||||||||||||||||||||||||||||||

| < < |

| ||||||||||||||||||||||||||||||||||||||||||||||

| > > |

| ||||||||||||||||||||||||||||||||||||||||||||||

| |||||||||||||||||||||||||||||||||||||||||||||||

| Changed: | |||||||||||||||||||||||||||||||||||||||||||||||

| < < |

| ||||||||||||||||||||||||||||||||||||||||||||||

| > > |

| ||||||||||||||||||||||||||||||||||||||||||||||

| Added: | |||||||||||||||||||||||||||||||||||||||||||||||

| > > |

| ||||||||||||||||||||||||||||||||||||||||||||||

| |||||||||||||||||||||||||||||||||||||||||||||||

| Added: | |||||||||||||||||||||||||||||||||||||||||||||||

| > > |

| ||||||||||||||||||||||||||||||||||||||||||||||

| |||||||||||||||||||||||||||||||||||||||||||||||

| Changed: | |||||||||||||||||||||||||||||||||||||||||||||||

| < < |

| ||||||||||||||||||||||||||||||||||||||||||||||

| > > |

| ||||||||||||||||||||||||||||||||||||||||||||||

| Added: | |||||||||||||||||||||||||||||||||||||||||||||||

| > > |

| ||||||||||||||||||||||||||||||||||||||||||||||

Tips

Comments

| |||||||||||||||||||||||||||||||||||||||||||||||

| Added: | |||||||||||||||||||||||||||||||||||||||||||||||

| > > |

| ||||||||||||||||||||||||||||||||||||||||||||||

Revision 122017-06-26 - AtlasjSilicon

RD53A DAQ DevelopmentIntroductionRD53 is a prospective ASIC for the HL-LHC upgrade. | |||||||||||||||||||||||||||||||||||||||||||||||

| Added: | |||||||||||||||||||||||||||||||||||||||||||||||

| > > | |||||||||||||||||||||||||||||||||||||||||||||||

/opt/Xilinx/Vivado/2016.4/data/xicom/cable_drivers/lin64/install_script/install_drivers sudo ./install_drivers | |||||||||||||||||||||||||||||||||||||||||||||||

| Changed: | |||||||||||||||||||||||||||||||||||||||||||||||

| < < | -- | ||||||||||||||||||||||||||||||||||||||||||||||

| > > | -- | ||||||||||||||||||||||||||||||||||||||||||||||

FE-I4 Readout Test | |||||||||||||||||||||||||||||||||||||||||||||||

| Changed: | |||||||||||||||||||||||||||||||||||||||||||||||

| < < |

| ||||||||||||||||||||||||||||||||||||||||||||||

| > > |

| ||||||||||||||||||||||||||||||||||||||||||||||

| Added: | |||||||||||||||||||||||||||||||||||||||||||||||

| > > |

| ||||||||||||||||||||||||||||||||||||||||||||||

Tips

Comments | |||||||||||||||||||||||||||||||||||||||||||||||

| Changed: | |||||||||||||||||||||||||||||||||||||||||||||||

| < < | |||||||||||||||||||||||||||||||||||||||||||||||

| > > | |||||||||||||||||||||||||||||||||||||||||||||||

| |||||||||||||||||||||||||||||||||||||||||||||||

Revision 112017-06-25 - AtlasjSilicon

RD53A DAQ DevelopmentIntroductionRD53 is a prospective ASIC for the HL-LHC upgrade. | |||||||||||||||||||||||||||||||||||||||||||||||

| Deleted: | |||||||||||||||||||||||||||||||||||||||||||||||

| < < | |||||||||||||||||||||||||||||||||||||||||||||||

/opt/Xilinx/Vivado/2016.4/data/xicom/cable_drivers/lin64/install_script/install_drivers sudo ./install_drivers-- FE-I4 Readout Test | |||||||||||||||||||||||||||||||||||||||||||||||

| Changed: | |||||||||||||||||||||||||||||||||||||||||||||||

| < < |

| ||||||||||||||||||||||||||||||||||||||||||||||

| > > |

| ||||||||||||||||||||||||||||||||||||||||||||||

| Added: | |||||||||||||||||||||||||||||||||||||||||||||||

| > > |

| ||||||||||||||||||||||||||||||||||||||||||||||

Tips

Comments

| |||||||||||||||||||||||||||||||||||||||||||||||

Revision 102017-06-15 - AtlasjSilicon

RD53A DAQ DevelopmentIntroductionRD53 is a prospective ASIC for the HL-LHC upgrade. | |||||||||||||||||||||||||||||||||||||||||||||||

| Added: | |||||||||||||||||||||||||||||||||||||||||||||||

| > > | |||||||||||||||||||||||||||||||||||||||||||||||

/opt/Xilinx/Vivado/2016.4/data/xicom/cable_drivers/lin64/install_script/install_drivers sudo ./install_drivers-- FE-I4 Readout Test | |||||||||||||||||||||||||||||||||||||||||||||||

| Changed: | |||||||||||||||||||||||||||||||||||||||||||||||

| < < |

| ||||||||||||||||||||||||||||||||||||||||||||||

| > > |

| ||||||||||||||||||||||||||||||||||||||||||||||

Tips

Comments

| |||||||||||||||||||||||||||||||||||||||||||||||

Revision 92017-06-13 - AtlasjSilicon

RD53A DAQ DevelopmentIntroductionRD53 is a prospective ASIC for the HL-LHC upgrade. | |||||||||||||||||||||||||||||||||||||||||||||||

| Deleted: | |||||||||||||||||||||||||||||||||||||||||||||||

| < < | |||||||||||||||||||||||||||||||||||||||||||||||

/opt/Xilinx/Vivado/2016.4/data/xicom/cable_drivers/lin64/install_script/install_drivers sudo ./install_drivers-- FE-I4 Readout Test | |||||||||||||||||||||||||||||||||||||||||||||||

| Changed: | |||||||||||||||||||||||||||||||||||||||||||||||

| < < |

| ||||||||||||||||||||||||||||||||||||||||||||||

| > > |

| ||||||||||||||||||||||||||||||||||||||||||||||

Tips

Comments

| |||||||||||||||||||||||||||||||||||||||||||||||

Revision 82017-06-12 - AtlasjSilicon

RD53A DAQ DevelopmentIntroductionRD53 is a prospective ASIC for the HL-LHC upgrade. | |||||||||||||||||||||||||||||||||||||||||||||||

| Added: | |||||||||||||||||||||||||||||||||||||||||||||||

| > > | |||||||||||||||||||||||||||||||||||||||||||||||

/opt/Xilinx/Vivado/2016.4/data/xicom/cable_drivers/lin64/install_script/install_drivers sudo ./install_drivers-- FE-I4 Readout Test | |||||||||||||||||||||||||||||||||||||||||||||||

| Changed: | |||||||||||||||||||||||||||||||||||||||||||||||

| < < |

| ||||||||||||||||||||||||||||||||||||||||||||||

| > > |

| ||||||||||||||||||||||||||||||||||||||||||||||

Tips

Comments

| |||||||||||||||||||||||||||||||||||||||||||||||

Revision 72017-06-06 - AtlasjSilicon

RD53A DAQ DevelopmentIntroductionRD53 is a prospective ASIC for the HL-LHC upgrade. | |||||||||||||||||||||||||||||||||||||||||||||||

| Deleted: | |||||||||||||||||||||||||||||||||||||||||||||||

| < < | |||||||||||||||||||||||||||||||||||||||||||||||

/opt/Xilinx/Vivado/2016.4/data/xicom/cable_drivers/lin64/install_script/install_drivers sudo ./install_drivers-- FE-I4 Readout Test | |||||||||||||||||||||||||||||||||||||||||||||||

| Changed: | |||||||||||||||||||||||||||||||||||||||||||||||

| < < |

| ||||||||||||||||||||||||||||||||||||||||||||||

| > > |

| ||||||||||||||||||||||||||||||||||||||||||||||

Tips

Comments

| |||||||||||||||||||||||||||||||||||||||||||||||

Revision 62017-05-26 - AtlasjSilicon

RD53A DAQ DevelopmentIntroductionRD53 is a prospective ASIC for the HL-LHC upgrade. | |||||||||||||||||||||||||||||||||||||||||||||

| Added: | |||||||||||||||||||||||||||||||||||||||||||||

| > > | |||||||||||||||||||||||||||||||||||||||||||||

/opt/Xilinx/Vivado/2016.4/data/xicom/cable_drivers/lin64/install_script/install_drivers sudo ./install_drivers-- FE-I4 Readout Test

| |||||||||||||||||||||||||||||||||||||||||||||

| Added: | |||||||||||||||||||||||||||||||||||||||||||||

| > > |

| ||||||||||||||||||||||||||||||||||||||||||||

Tips

Comments

| |||||||||||||||||||||||||||||||||||||||||||||

| Added: | |||||||||||||||||||||||||||||||||||||||||||||

| > > |

| ||||||||||||||||||||||||||||||||||||||||||||

Revision 52017-05-25 - AtlasjSilicon

RD53A DAQ DevelopmentIntroductionRD53 is a prospective ASIC for the HL-LHC upgrade./opt/Xilinx/Vivado/2016.4/data/xicom/cable_drivers/lin64/install_script/install_drivers sudo ./install_drivers | |||||||||||||||||||||||||||||||||||||||||||||

| Changed: | |||||||||||||||||||||||||||||||||||||||||||||

| < < | -- | ||||||||||||||||||||||||||||||||||||||||||||

| > > | -- | ||||||||||||||||||||||||||||||||||||||||||||

FE-I4 Readout Test

| |||||||||||||||||||||||||||||||||||||||||||||

| Added: | |||||||||||||||||||||||||||||||||||||||||||||

| > > |

Tips

| ||||||||||||||||||||||||||||||||||||||||||||

Comments | |||||||||||||||||||||||||||||||||||||||||||||

| Changed: | |||||||||||||||||||||||||||||||||||||||||||||

| < < | |||||||||||||||||||||||||||||||||||||||||||||

| > > | |||||||||||||||||||||||||||||||||||||||||||||

| Added: | |||||||||||||||||||||||||||||||||||||||||||||

| > > |

| ||||||||||||||||||||||||||||||||||||||||||||

Revision 42017-05-17 - AtlasjSilicon

RD53A DAQ DevelopmentIntroductionRD53 is a prospective ASIC for the HL-LHC upgrade. | ||||||||

| Deleted: | ||||||||

| < < | ||||||||

/opt/Xilinx/Vivado/2016.4/data/xicom/cable_drivers/lin64/install_script/install_drivers sudo ./install_drivers-- | ||||||||

| Added: | ||||||||

| > > | FE-I4 Readout Test

| |||||||

Comments | ||||||||

Revision 32017-04-19 - KojiNakamura

RD53A DAQ DevelopmentIntroductionRD53 is a prospective ASIC for the HL-LHC upgrade. | ||||||||

| Added: | ||||||||

| > > |

/opt/Xilinx/Vivado/2016.4/data/xicom/cable_drivers/lin64/install_script/install_drivers sudo ./install_drivers | |||||||

-- Comments | ||||||||

Revision 22016-10-17 - AtlasjSilicon

RD53A DAQ Development | ||||||||

| Added: | ||||||||

| > > | Introduction | |||||||

| Changed: | ||||||||

| < < | Article text. | |||||||

| > > | RD53 is a prospective ASIC for the HL-LHC upgrade. | |||||||

| Changed: | ||||||||

| < < | -- | |||||||

| > > | -- | |||||||

Comments | ||||||||

| Changed: | ||||||||

| < < | ||||||||

| > > | ||||||||

Revision 12016-10-11 - AtlasjSilicon

RD53A DAQ DevelopmentArticle text. --Comments |

Ideas, requests, problems regarding TWiki? Send feedback