RD53A DAQ Development

Introduction

RD53 is a prospective ASIC for the HL-LHC upgrade./opt/Xilinx/Vivado/2016.4/data/xicom/cable_drivers/lin64/install_script/install_drivers sudo ./install_drivers--

FE-I4 Readout Test

- FPGA Hardware and Additional apparatuses

- FPGA Hardware

- Prerequisites

Target devices : Virtex-7 VC707 Evaluation Platform (xc7vx485tffg1761-2)

Tool Version : Xilinx Vivado 2015.4 or later tools

If you are using Kintex-7 KC705 Evaluation Platform, you need to change the SiTCP module in the firmware to XC7KSiTCPlib32k.

- Prerequisites

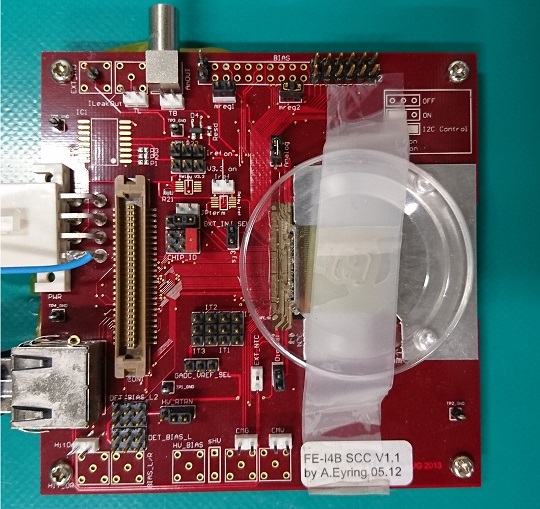

- FEI4B Single Chip Card

- Manual FE-I4B_V2.0.pdf

-

-

- Appearance

- Manual FE-I4B_V2.0.pdf

- RJ45/FMC - SLVS/LVDS Conversion Board

- TB-FMCL-PH board (inrevium TOKYO ELECTRON DEVICE)

- used for conversion between Samtec FMC connector (Low-Pin Count) and 2.54mm pitch pin header. - SLVS <-> LVDS level shiter designed by Ryo Nagai: LVDS2SLVS_Pins.zip

- TB-FMCL-PH board (inrevium TOKYO ELECTRON DEVICE)

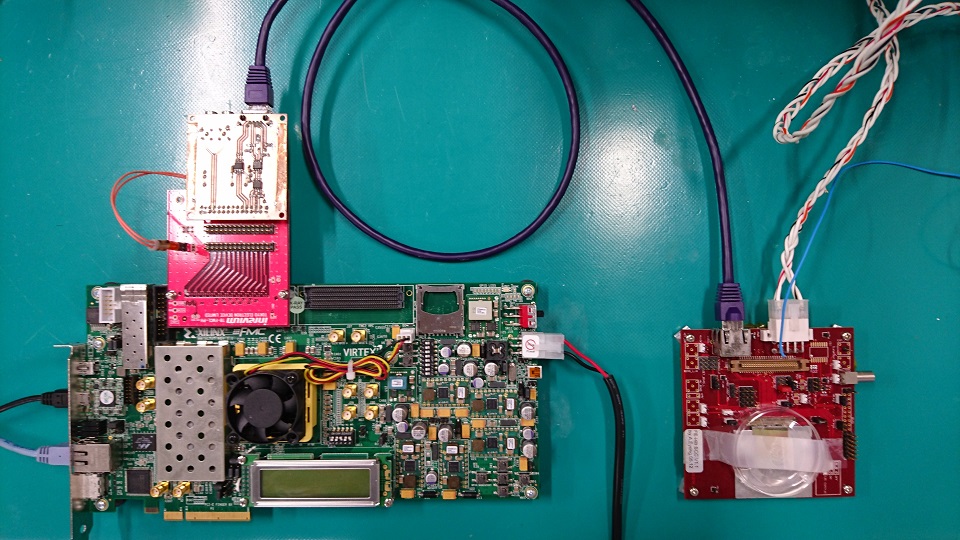

- Hardware setup

- Example recipe

- Power supply for SEABAS2

- VDDA: +1.5 V, current limit 0.7 A

- VDDD: +1.5 V, current limit 0.4 A (Not : 1.2 V!!)

- Ethernet cable x2 (To use 1000BASE-T, use a Cat 5 cable or later. One between a conversion board and a SCC should be metal shielded to match GNDs.)

- SourceMeter for the silicon sensor

- Power supply for SEABAS2

- Example recipe

- FPGA Hardware

- DAQ Software

- SEABAS DAQ for ATLAS Pixel Upgrade

- source : trunk/multi_chip_FEI4/Software_SEABAS2

- SiTCP IP Address : Default (192.168.10.16)

- How to config FEI4

- For example, execute on your terminal run 1 0111 which is a command to do "Digital Injection and mask chip_1 to chip3."

Please refer to SEABAS2 DAQ Usages .

.

- For example, execute on your terminal run 1 0111 which is a command to do "Digital Injection and mask chip_1 to chip3."

- SEABAS DAQ for ATLAS Pixel Upgrade

- Release

- Firmware for VC707 to readout FE-I4B SCC - 2017.06.26 (Sawada.Y)

- Seabas2VC707_20170626.xpr.zip - Suppress critical warnings due to timing violations...

- Suppress critical warnings due to timing violations...

- Seabas2VC707_part1_20170615.xpr.zip - corrected to output RunMode command signal.

- Firmware for VC707 to readout FE-I4B SCC - 2017.06.26 (Sawada.Y)

- Notes

- When you use the original conversion board, you need to change the pin assignment to comply with your board.

(Default firmware is build for a setup of Osaka Univ.) - Already-known warnings

- Redundant IBUF can be ignored. "Could not create 'IBUF_LOW_PWR' constraint because ..." and "Removing redundant IBUF since ..." can be ignored.

- Unused registers.

- Programming VC707 Virtex7 BPI Flash memory

- Generate a bitstream (.bit) file in the normal way.

- Run this TCL command inside Vivado:

$ write_cfgmem -format mcs -interface bpix16 -size 128 -loadbit "up 0x0 /path/to/bitfile.bit" -file mynewmcs.mcs - Open Vivado Lab Edition

- Open Hardware Manager, open target board

- Tools > Add Configuration Memory Device

- Select this part:

Name: mt28gu01gaax1e-bpi-x16

Part: mt28gu01gaax1e

Manufacturer: Micron

Alias: 28f00ag18f

Family: g18

Type: bpi

Density: 1024

Width: x16 - Click OK to "Do you want to program the configuration memory device now?"

- Add your .mcs file to the Configuration File field

- Hit OK

- Right click on device >> Boot from Configuration Memory Device

- Change the VC707 FPGA Board Configuration Mode JTAG to Master BPI. Set SW13 DIP switch M[2:0]=010.

- Status report

- (6/29 12:00) It is found that DataStore module is bottleneck for readout data... by Sawada

- (6/28 16:00) Previous problem was solved. "KEEP HIERARCHY" attribute is needed to not to change the hirarchy when Vivado synthesis.

- (6/28 10:00) IserdesWith8b10bDec has a bug. Problem is still not be found. Maybe 8b10b decoder module is not removed when running synthesis... by Sawada

- (6/26) Succeeded in configuring FE-I4B and confirmed the response of the data signal. Problems remain in iserdes, 8b10b decoder part. by Sawada

- When you use the original conversion board, you need to change the pin assignment to comply with your board.

Tips

- Text on FPGA training

- prepapration: OFTC_preparation.pdf

-

main body: OFTC_0.pdf, OFTC_1.pdf, OFTC_2_1.pdf, OFTC_2_2.pdf, OFTC_2_3.pdf, OFTC_2_4.pdf, OFTC_3.pdf, OFTC_4_1.pdf, OFTC_4_2.pdf, OFTC_4_3.pdf, OFTC_5.pdf, OFTC_6.pdf, OFTC_7.pdf, OFTC_8.pdf, OFTC_9.pdf

- training course: OFTC_lab_c1_rev20.pdf, OFTC_lab_s1_rev20.pdf, OFTC_lab_i1_rev11.pdf, OFTC_lab_i2_rev13.pdf

- reference: OFTC_ref_note.pdf, references.pdf

- Useful links

Comments

| I | Attachment | History | Action | Size | Date | Who | Comment |

|---|---|---|---|---|---|---|---|

| |

LVDS2SLVS_Pins.zip | r1 | manage | 212.2 K | 2017-05-26 - 10:16 | AtlasjSilicon | |

| |

OFTC_0.pdf | r1 | manage | 605.1 K | 2017-05-25 - 05:43 | AtlasjSilicon | |

| |

OFTC_1.pdf | r1 | manage | 1740.3 K | 2017-05-25 - 05:44 | AtlasjSilicon | |

| |

OFTC_2_1.pdf | r1 | manage | 698.8 K | 2017-05-25 - 05:44 | AtlasjSilicon | |

| |

OFTC_2_2.pdf | r1 | manage | 2387.5 K | 2017-05-25 - 05:44 | AtlasjSilicon | |

| |

OFTC_2_3.pdf | r1 | manage | 1986.6 K | 2017-05-25 - 05:44 | AtlasjSilicon | |

| |

OFTC_2_4.pdf | r1 | manage | 4259.7 K | 2017-05-25 - 05:44 | AtlasjSilicon | |

| |

OFTC_3.pdf | r1 | manage | 717.2 K | 2017-05-25 - 05:44 | AtlasjSilicon | |

| |

OFTC_4_1.pdf | r1 | manage | 448.6 K | 2017-05-25 - 05:44 | AtlasjSilicon | |

| |

OFTC_4_2.pdf | r1 | manage | 2451.2 K | 2017-05-25 - 05:44 | AtlasjSilicon | |

| |

OFTC_4_3.pdf | r1 | manage | 2801.5 K | 2017-05-25 - 05:44 | AtlasjSilicon | |

| |

OFTC_5.pdf | r1 | manage | 384.8 K | 2017-05-25 - 05:45 | AtlasjSilicon | |

| |

OFTC_6.pdf | r1 | manage | 1347.2 K | 2017-05-25 - 05:45 | AtlasjSilicon | |

| |

OFTC_7.pdf | r1 | manage | 3128.1 K | 2017-05-25 - 05:45 | AtlasjSilicon | |

| |

OFTC_8.pdf | r1 | manage | 695.8 K | 2017-05-25 - 05:45 | AtlasjSilicon | |

| |

OFTC_9.pdf | r1 | manage | 1439.0 K | 2017-05-25 - 05:45 | AtlasjSilicon | |

| |

OFTC_lab_c1_rev20.pdf | r1 | manage | 122.7 K | 2017-05-25 - 05:45 | AtlasjSilicon | |

| |

OFTC_lab_i1_rev11.pdf | r1 | manage | 105.8 K | 2017-05-25 - 05:45 | AtlasjSilicon | |

| |

OFTC_lab_i2_rev13.pdf | r1 | manage | 104.8 K | 2017-05-25 - 05:45 | AtlasjSilicon | |

| |

OFTC_lab_s1_rev20.pdf | r1 | manage | 131.0 K | 2017-05-25 - 05:45 | AtlasjSilicon | |

| |

OFTC_preparation.pdf | r1 | manage | 2018.1 K | 2017-05-25 - 05:46 | AtlasjSilicon | |

| |

OFTC_ref_note.pdf | r1 | manage | 47.7 K | 2017-05-25 - 05:46 | AtlasjSilicon | |

| |

references.pdf | r1 | manage | 871.8 K | 2017-05-25 - 06:19 | AtlasjSilicon |

Topic revision: r18 - 2017-06-29 - AtlasjSilicon

Ideas, requests, problems regarding TWiki? Send feedback