Difference: FE65p2ChipDAQ (1 vs. 30)

Revision 302017-12-08 - KojiNakamura

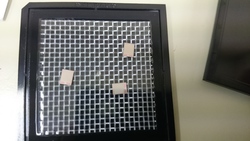

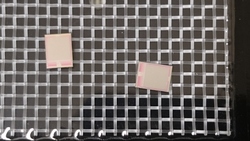

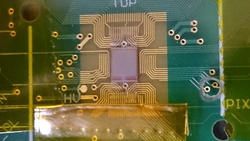

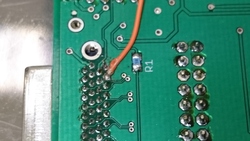

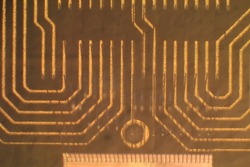

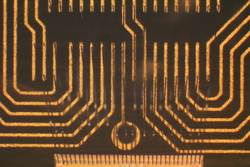

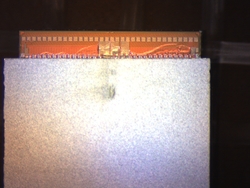

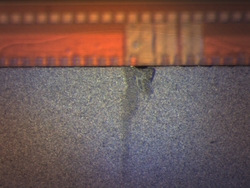

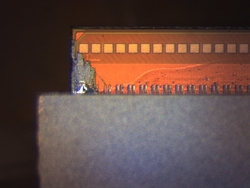

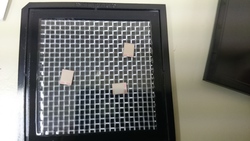

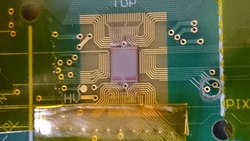

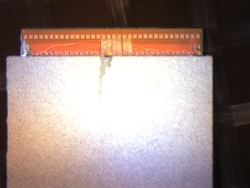

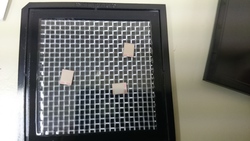

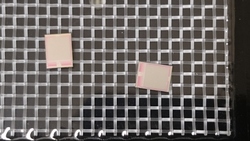

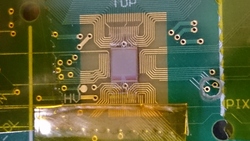

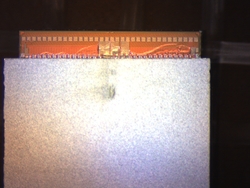

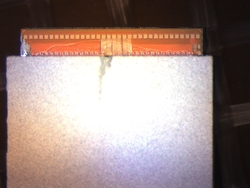

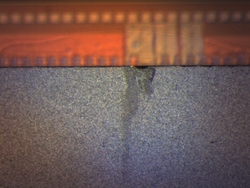

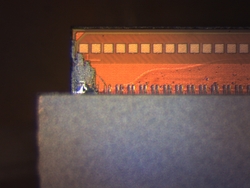

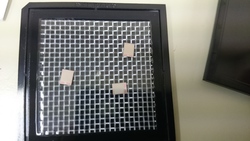

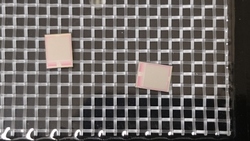

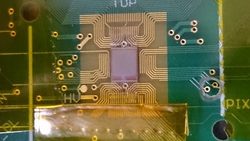

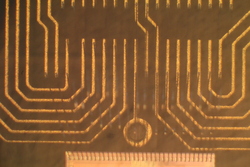

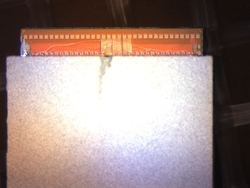

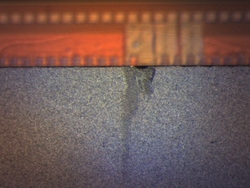

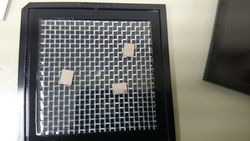

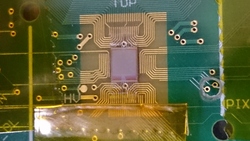

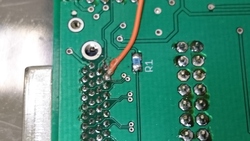

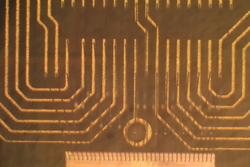

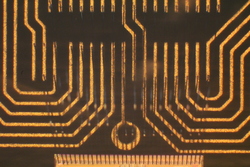

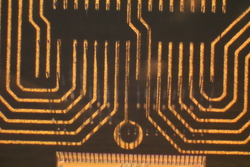

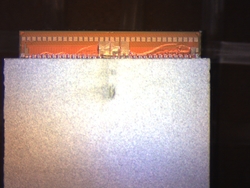

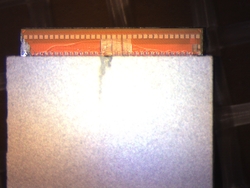

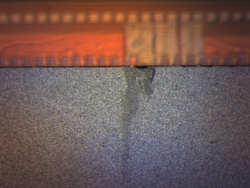

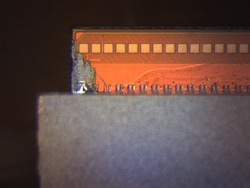

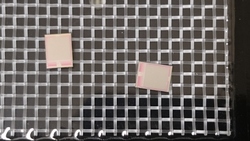

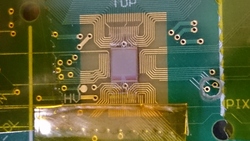

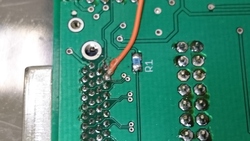

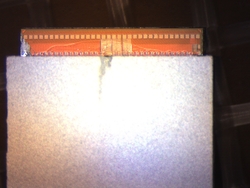

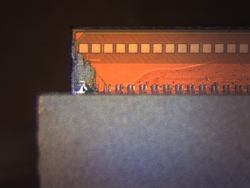

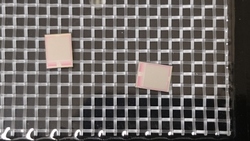

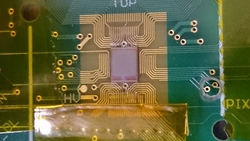

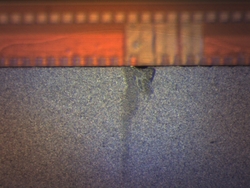

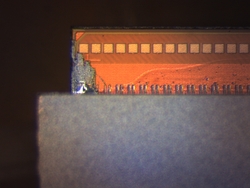

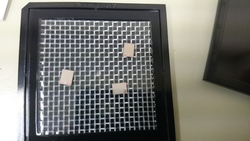

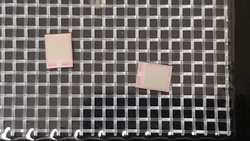

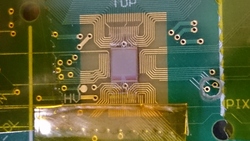

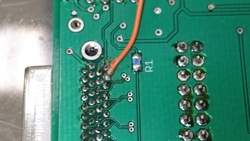

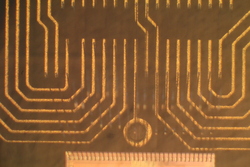

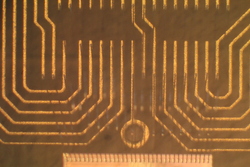

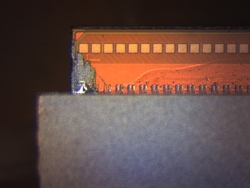

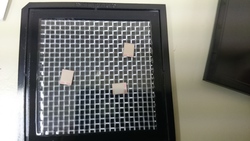

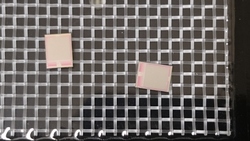

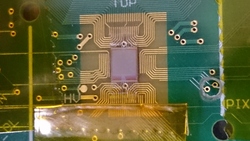

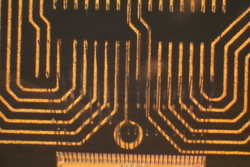

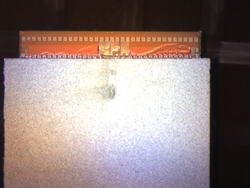

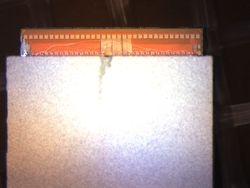

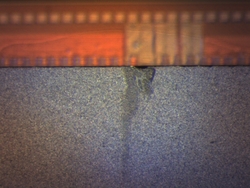

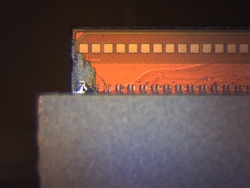

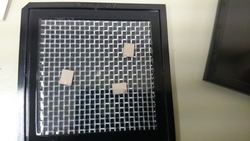

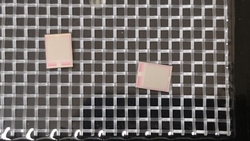

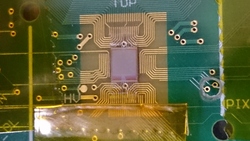

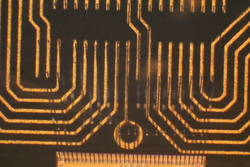

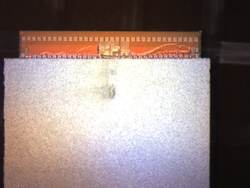

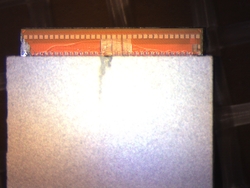

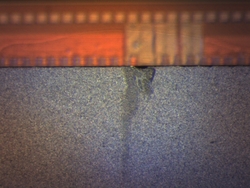

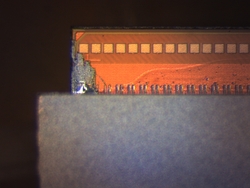

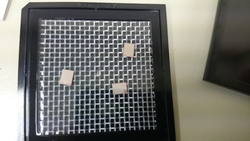

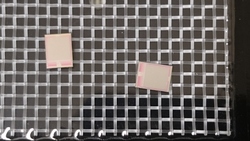

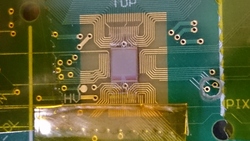

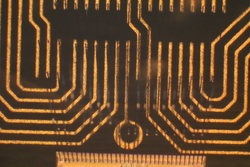

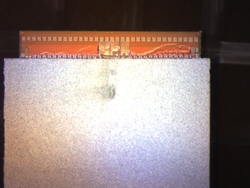

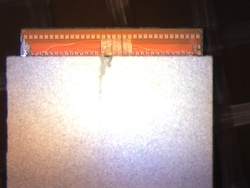

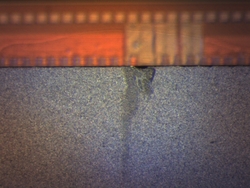

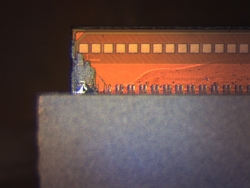

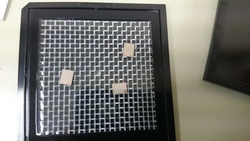

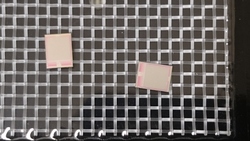

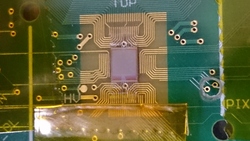

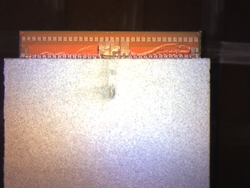

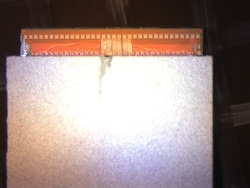

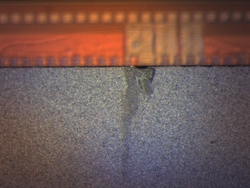

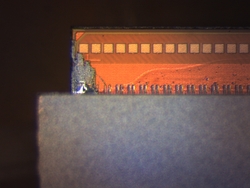

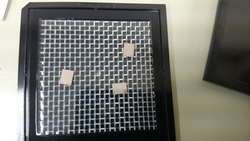

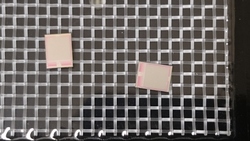

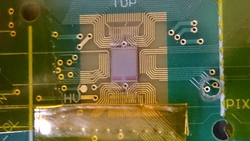

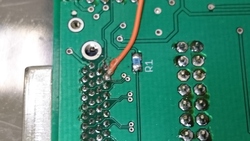

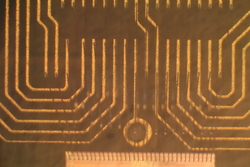

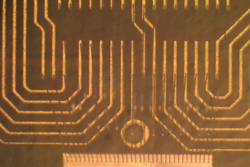

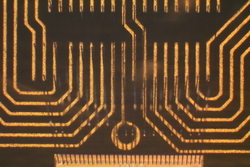

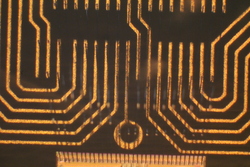

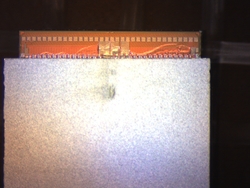

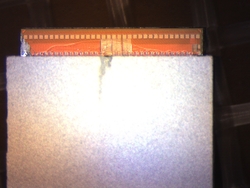

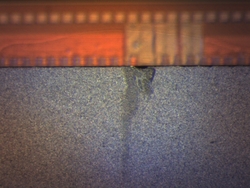

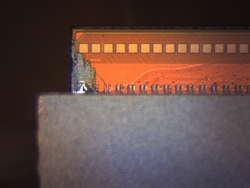

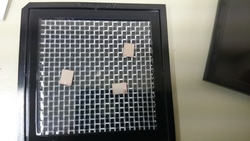

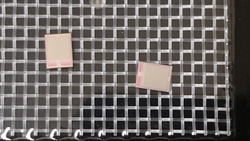

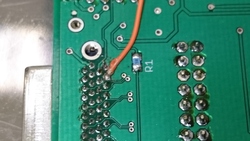

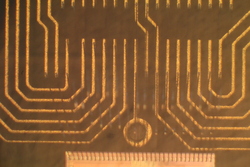

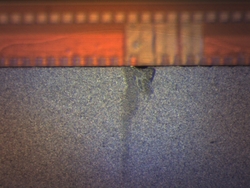

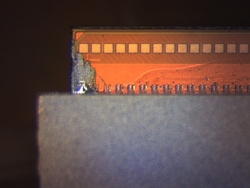

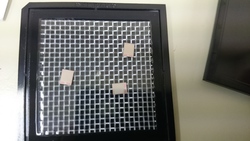

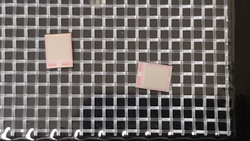

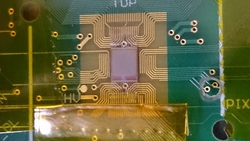

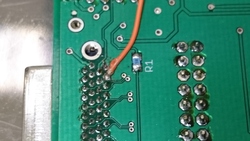

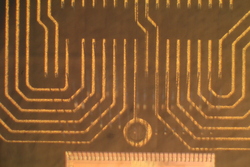

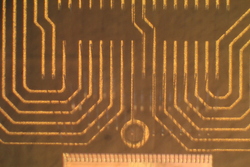

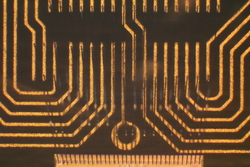

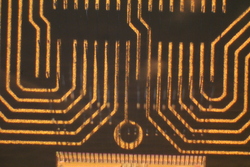

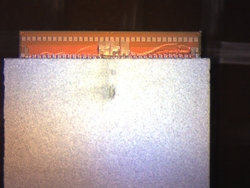

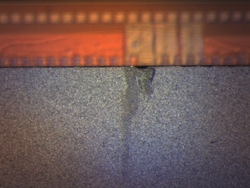

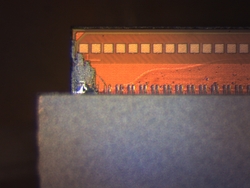

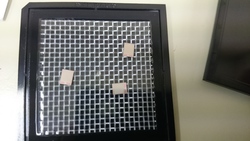

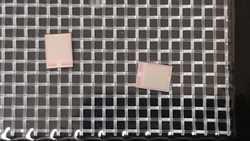

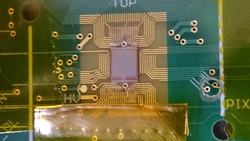

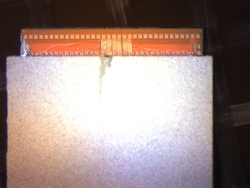

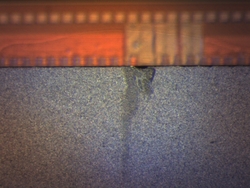

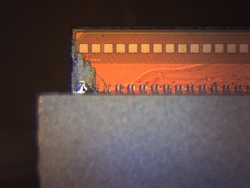

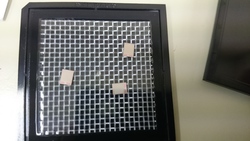

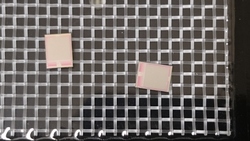

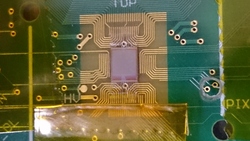

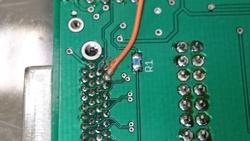

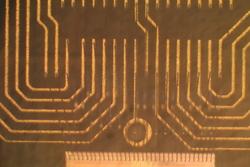

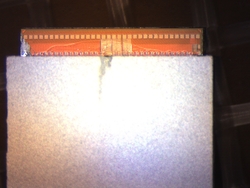

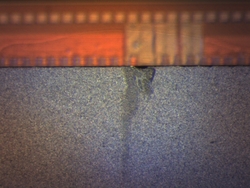

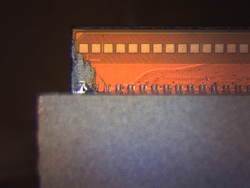

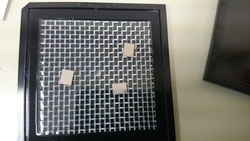

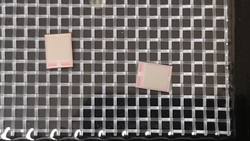

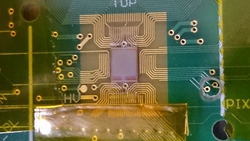

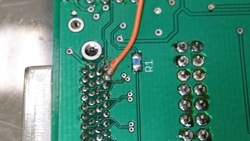

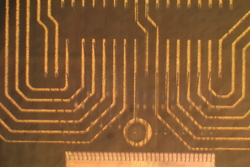

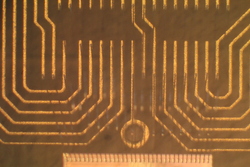

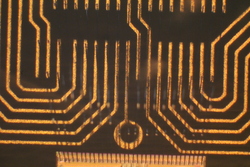

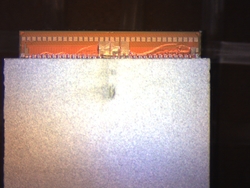

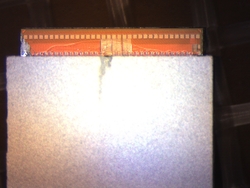

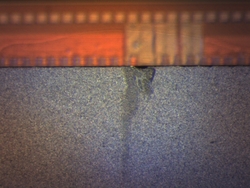

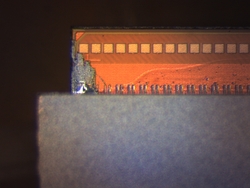

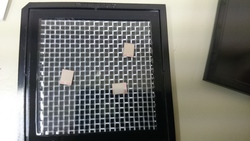

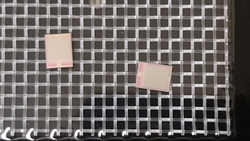

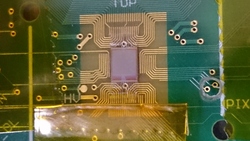

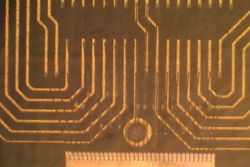

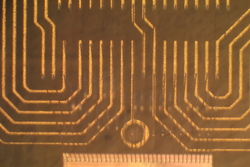

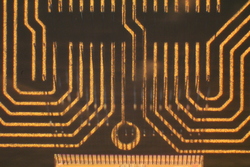

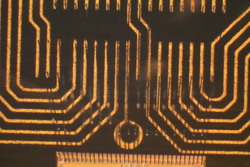

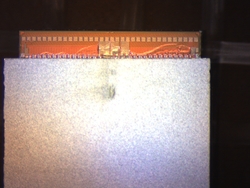

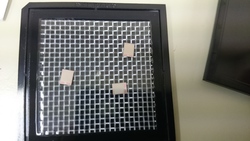

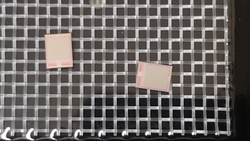

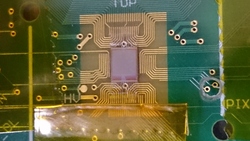

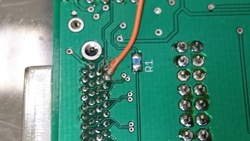

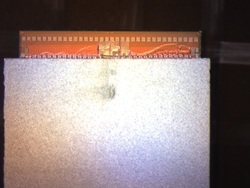

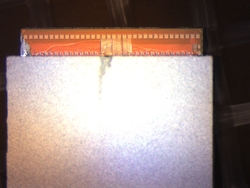

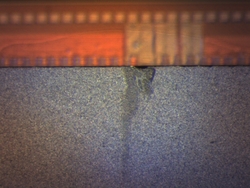

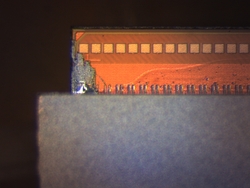

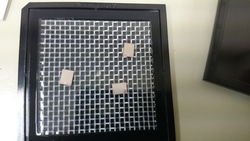

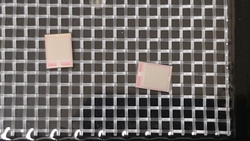

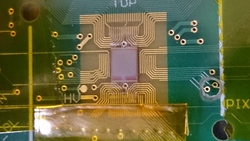

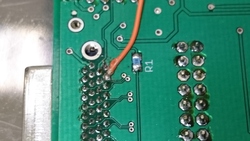

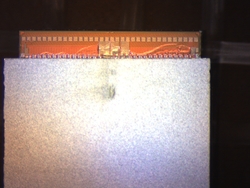

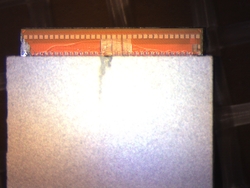

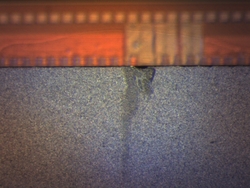

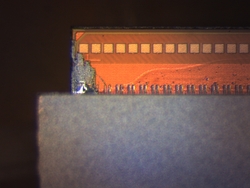

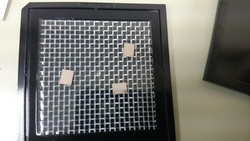

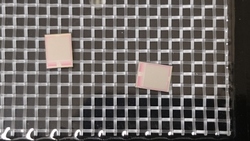

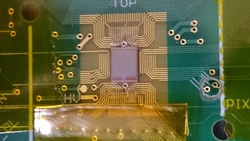

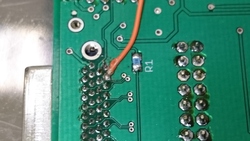

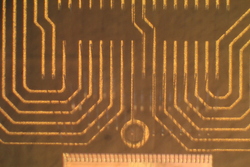

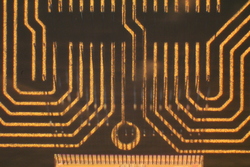

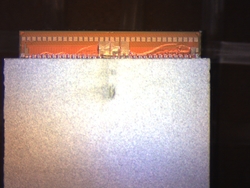

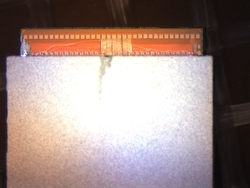

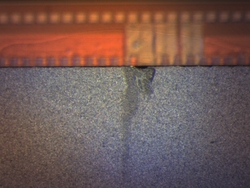

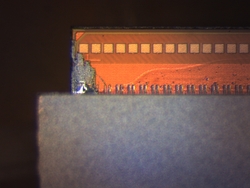

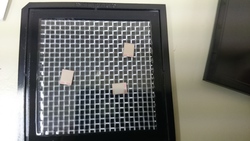

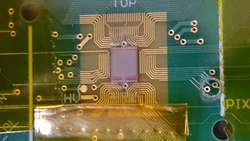

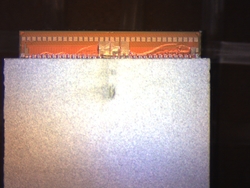

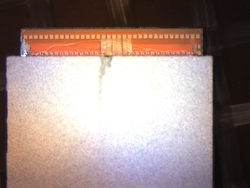

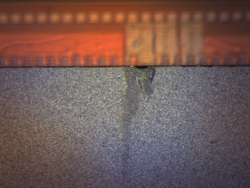

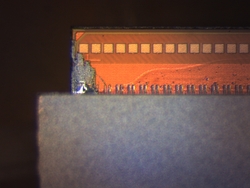

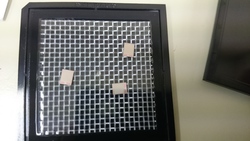

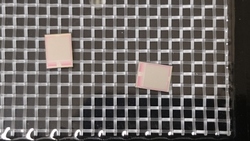

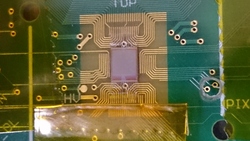

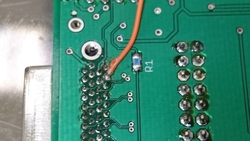

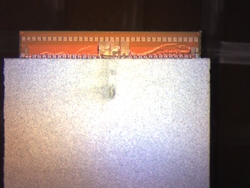

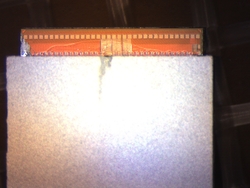

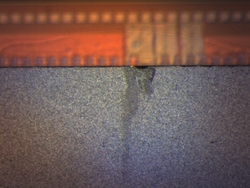

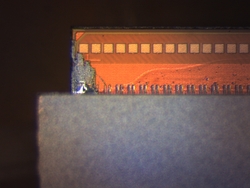

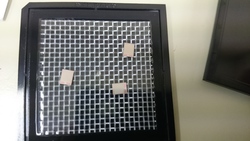

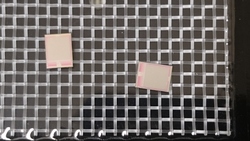

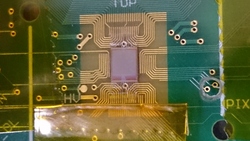

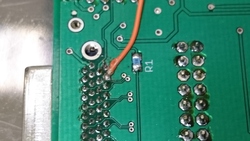

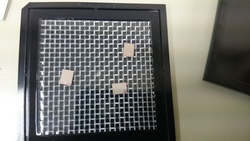

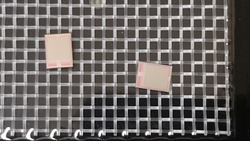

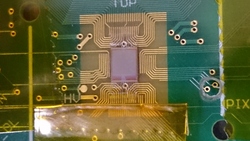

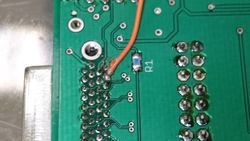

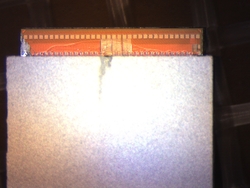

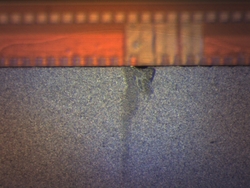

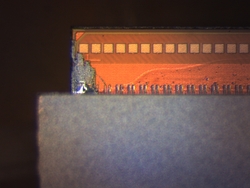

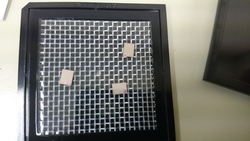

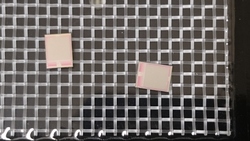

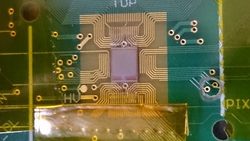

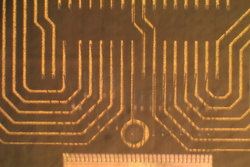

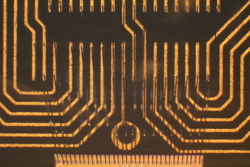

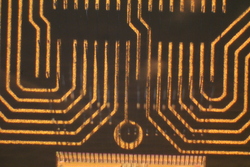

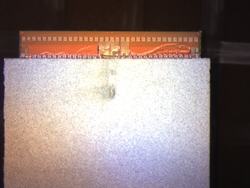

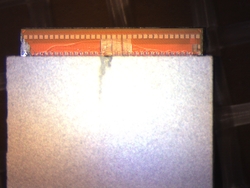

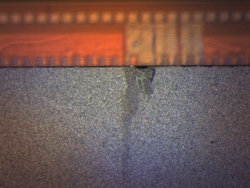

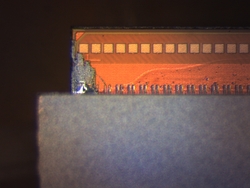

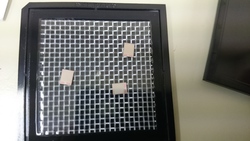

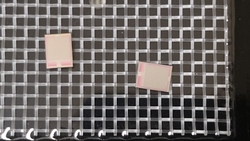

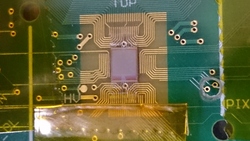

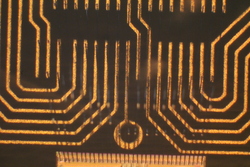

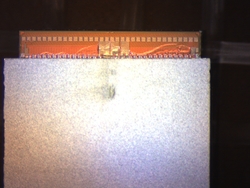

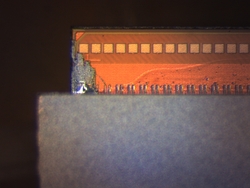

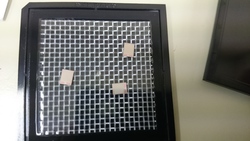

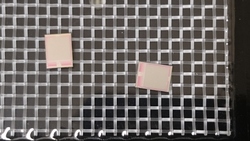

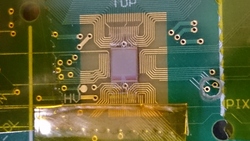

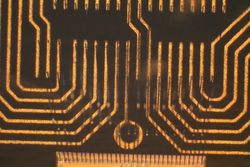

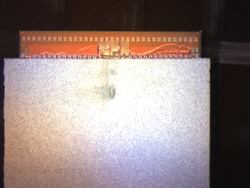

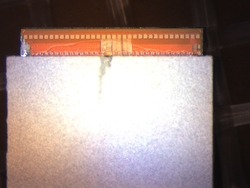

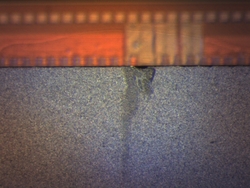

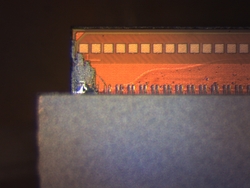

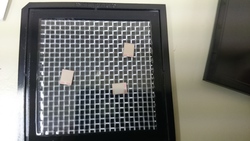

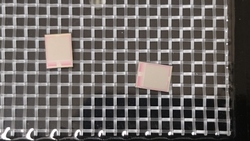

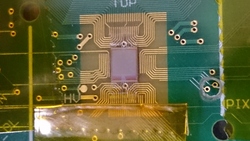

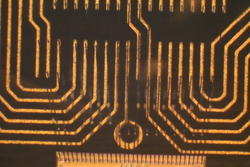

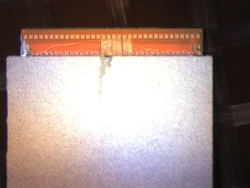

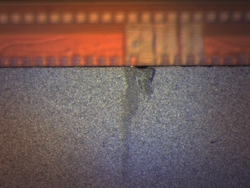

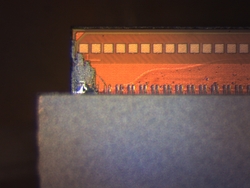

DAQ development for FE65-P2 chipIntroductionFE65-P2 is the readout ASIC with 65nm processing as pre-pre-production for the RD53A/B chips used by HL-LHC ITK pixel upgrade. more information is available in : motivation talk in AUW April 2016Chips and Bump Bonding at SLACsensor name,bias(type), condition, patch work, dose,

DAQ development by SPEC

How to setup SPEC board

mkdir -p /home/atlasj/work/SPEC/YARR cd /home/atlasj/work/SPEC/YARR/ git clone https://github.com/Yarr/Yarr.git git fetch git checkout fe65_p2 cd /home/atlasj/work/SPEC/YARR/Yarr/src/kernel make sudo make install sudo depmod cd ../ ; make

sudo modprobe specDriver bin/programFpga ../hdl/syn/yarr_fe65p2_revB.bit bin/test bin/benchmarkDma How to configure chips and run scantuning

General scan consolHitOr self trigger scan1. Run digital scan2. Run analog scan 3. Prepare config: - Enable all pixels: # bin/config_fe65-p2 fe65p2.json (Overwrites config file) - Apply digital scan mask: # bin/applyMask fe65p2_ch0_digitalscan_EnMask.dat fe65p2.json - Copy masked config: # cp masked_fe65p2.json fe65p2.json - Apply analog scan mask: # bin/applyMask fe65p2_ch0_analogscan_EnMask.dat fe65p2.json - Copy masked config: # cp masked_fe65p2.json fe65p2.json 4. Run noise scan (~5min) 5. Apply noise mask: - Apply digital scan mask: # bin/applyMask fe65p2_ch0_noisescan_NoiseMask.dat fe65p2.json - Copy masked config: # cp masked_fe65p2.json fe65p2.json 6. Mask stuck/noise hitter pixels: - #bin/fixHitbus fe65p2.json (takes quite some time ~15min) - Only pixels which will get masked get printed to stdout, optimally these should not be many - If many pixels appear to not work something is wrong - You can observe the process by probing HitOr Output and Trigger, there should be two hitOr pulses per trigger - The program produces a mask hitbus_enMask.png - Copy masked config: # cp masked_fe65p2.json fe65p2.json 7. Run exttrigger scan: - If everything went right you should observe a trigger rate of a few Hz without a particle source - With source the rate should be much higher - The internal dead time is 200bc (currently hardcoded for testing) YARR DAQ in EUDAQHi Koji, See here for instructions on eudaq: http://yarr.readthedocs.io/en/eudaq/eudaq.html Swap into branch eudaq. Dont forget to program the correct firmware (assuming you already have the adapter board). Some remarks: - I had a merge conflict problem in the firmware and Im not 100% that is resolvers properly. If it is not right, YARR would not answer to triggers, which you should see if the RC does not see more trigger. - I had to change the way events get send to the RC, this is untested and I hope it works. - There is a version of the converter, but Im sure there were local changes and I cant get onto the eudaq machine at SLAC due to some stupid permissions. We need to wait until someone sends me the file. If you give me a not to random time window in your night where I can test some things with, we could do that. I have to run some errants and will not be at my laptop the whole time. Otherwise we can get everything running once Im there in person. Cheers, Timonhttps://eutelescope.web.cern.ch/forum/multiple-dut-events-tlu-trigger Exttrigger modeSeabas firmware :MPPC bias : ~60V Latency : 70 ///// memo KEKFE65-13@-20degC CompVbnDac: 50 PrempVbpDac: 120 VbnLccDac : 200 VffDac : 15 | |||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

| Added: | |||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

| > > |

XpressK7 DAQFE65byXpressK7 | ||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

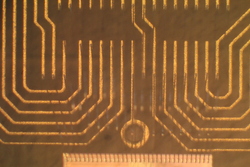

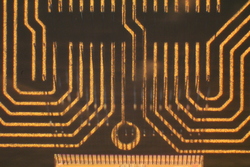

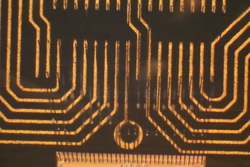

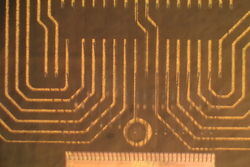

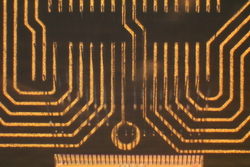

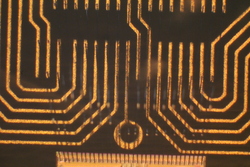

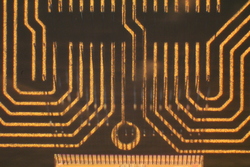

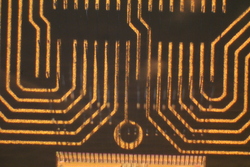

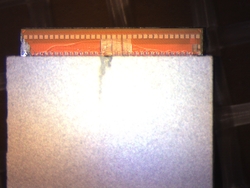

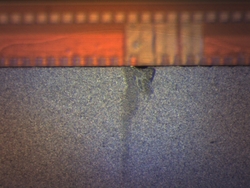

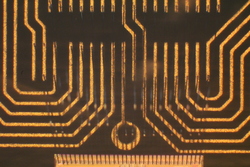

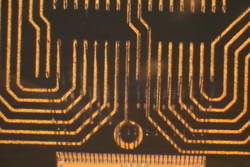

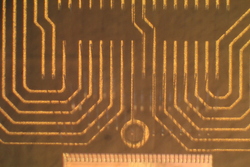

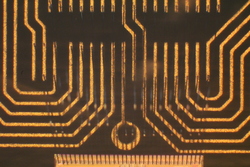

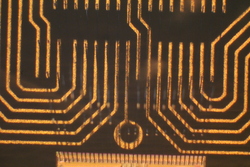

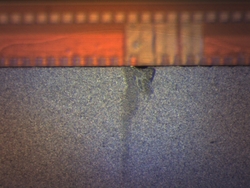

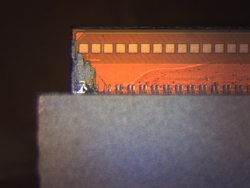

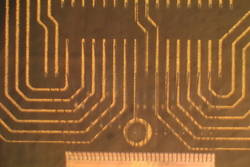

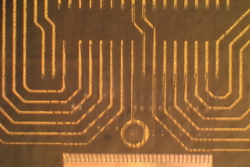

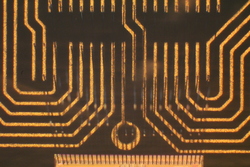

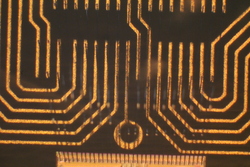

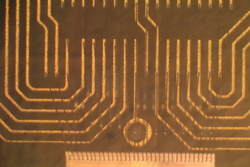

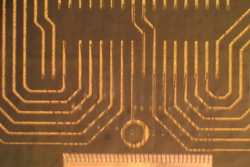

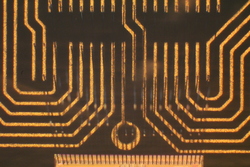

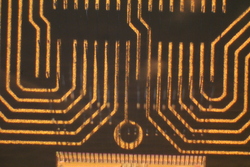

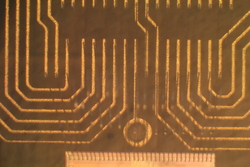

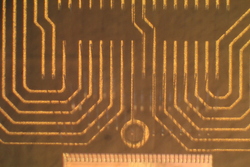

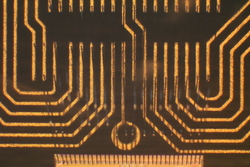

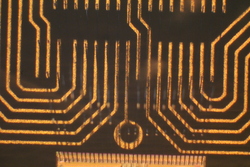

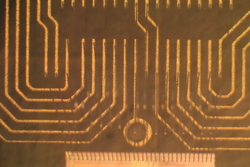

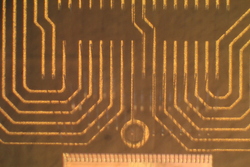

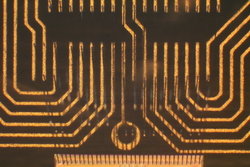

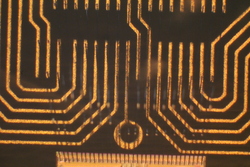

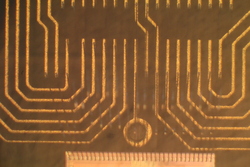

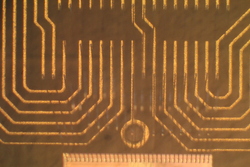

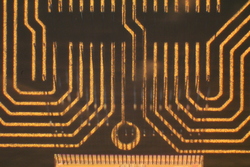

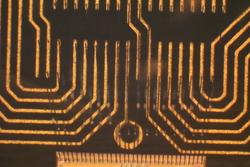

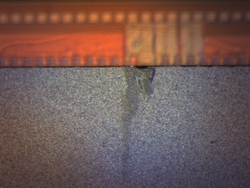

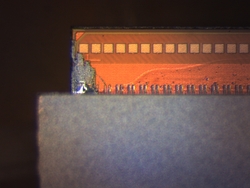

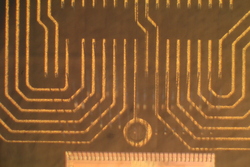

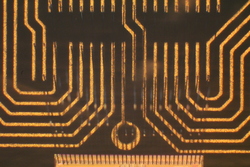

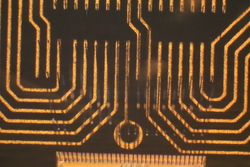

ImagesThere are 24 images in this page -- Log noteAfterIrrad20161018

| |||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

Revision 292017-10-17 - AtlasjSilicon

DAQ development for FE65-P2 chipIntroductionFE65-P2 is the readout ASIC with 65nm processing as pre-pre-production for the RD53A/B chips used by HL-LHC ITK pixel upgrade. more information is available in : motivation talk in AUW April 2016Chips and Bump Bonding at SLACsensor name,bias(type), condition, patch work, dose,

| |||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

| Changed: | |||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

| < < | |||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

| > > |

| ||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

| Added: | |||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

| > > |

| ||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

DAQ development by SPEC

How to setup SPEC board

mkdir -p /home/atlasj/work/SPEC/YARR cd /home/atlasj/work/SPEC/YARR/ git clone https://github.com/Yarr/Yarr.git git fetch git checkout fe65_p2 cd /home/atlasj/work/SPEC/YARR/Yarr/src/kernel make sudo make install sudo depmod cd ../ ; make

sudo modprobe specDriver bin/programFpga ../hdl/syn/yarr_fe65p2_revB.bit bin/test bin/benchmarkDma How to configure chips and run scantuning

General scan consolHitOr self trigger scan1. Run digital scan2. Run analog scan 3. Prepare config: - Enable all pixels: # bin/config_fe65-p2 fe65p2.json (Overwrites config file) - Apply digital scan mask: # bin/applyMask fe65p2_ch0_digitalscan_EnMask.dat fe65p2.json - Copy masked config: # cp masked_fe65p2.json fe65p2.json - Apply analog scan mask: # bin/applyMask fe65p2_ch0_analogscan_EnMask.dat fe65p2.json - Copy masked config: # cp masked_fe65p2.json fe65p2.json 4. Run noise scan (~5min) 5. Apply noise mask: - Apply digital scan mask: # bin/applyMask fe65p2_ch0_noisescan_NoiseMask.dat fe65p2.json - Copy masked config: # cp masked_fe65p2.json fe65p2.json 6. Mask stuck/noise hitter pixels: - #bin/fixHitbus fe65p2.json (takes quite some time ~15min) - Only pixels which will get masked get printed to stdout, optimally these should not be many - If many pixels appear to not work something is wrong - You can observe the process by probing HitOr Output and Trigger, there should be two hitOr pulses per trigger - The program produces a mask hitbus_enMask.png - Copy masked config: # cp masked_fe65p2.json fe65p2.json 7. Run exttrigger scan: - If everything went right you should observe a trigger rate of a few Hz without a particle source - With source the rate should be much higher - The internal dead time is 200bc (currently hardcoded for testing) YARR DAQ in EUDAQHi Koji, See here for instructions on eudaq: http://yarr.readthedocs.io/en/eudaq/eudaq.html Swap into branch eudaq. Dont forget to program the correct firmware (assuming you already have the adapter board). Some remarks: - I had a merge conflict problem in the firmware and Im not 100% that is resolvers properly. If it is not right, YARR would not answer to triggers, which you should see if the RC does not see more trigger. - I had to change the way events get send to the RC, this is untested and I hope it works. - There is a version of the converter, but Im sure there were local changes and I cant get onto the eudaq machine at SLAC due to some stupid permissions. We need to wait until someone sends me the file. If you give me a not to random time window in your night where I can test some things with, we could do that. I have to run some errants and will not be at my laptop the whole time. Otherwise we can get everything running once Im there in person. Cheers, Timonhttps://eutelescope.web.cern.ch/forum/multiple-dut-events-tlu-trigger Exttrigger modeSeabas firmware :MPPC bias : ~60V Latency : 70 ///// memo KEKFE65-13@-20degC CompVbnDac: 50 PrempVbpDac: 120 VbnLccDac : 200 VffDac : 15 ImagesThere are 24 images in this page -- Log noteAfterIrrad20161018

| |||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

Revision 282017-07-05 - JunkiSuzuki

DAQ development for FE65-P2 chipIntroductionFE65-P2 is the readout ASIC with 65nm processing as pre-pre-production for the RD53A/B chips used by HL-LHC ITK pixel upgrade. more information is available in : motivation talk in AUW April 2016Chips and Bump Bonding at SLACsensor name,bias(type), condition, patch work, dose,

DAQ development by SPEC

How to setup SPEC board

mkdir -p /home/atlasj/work/SPEC/YARR cd /home/atlasj/work/SPEC/YARR/ git clone https://github.com/Yarr/Yarr.git git fetch git checkout fe65_p2 cd /home/atlasj/work/SPEC/YARR/Yarr/src/kernel make sudo make install sudo depmod cd ../ ; make

sudo modprobe specDriver bin/programFpga ../hdl/syn/yarr_fe65p2_revB.bit bin/test bin/benchmarkDma How to configure chips and run scantuning

General scan consolHitOr self trigger scan1. Run digital scan2. Run analog scan 3. Prepare config: - Enable all pixels: # bin/config_fe65-p2 fe65p2.json (Overwrites config file) - Apply digital scan mask: # bin/applyMask fe65p2_ch0_digitalscan_EnMask.dat fe65p2.json - Copy masked config: # cp masked_fe65p2.json fe65p2.json - Apply analog scan mask: # bin/applyMask fe65p2_ch0_analogscan_EnMask.dat fe65p2.json - Copy masked config: # cp masked_fe65p2.json fe65p2.json 4. Run noise scan (~5min) 5. Apply noise mask: - Apply digital scan mask: # bin/applyMask fe65p2_ch0_noisescan_NoiseMask.dat fe65p2.json - Copy masked config: # cp masked_fe65p2.json fe65p2.json 6. Mask stuck/noise hitter pixels: - #bin/fixHitbus fe65p2.json (takes quite some time ~15min) - Only pixels which will get masked get printed to stdout, optimally these should not be many - If many pixels appear to not work something is wrong - You can observe the process by probing HitOr Output and Trigger, there should be two hitOr pulses per trigger - The program produces a mask hitbus_enMask.png - Copy masked config: # cp masked_fe65p2.json fe65p2.json 7. Run exttrigger scan: - If everything went right you should observe a trigger rate of a few Hz without a particle source - With source the rate should be much higher - The internal dead time is 200bc (currently hardcoded for testing) YARR DAQ in EUDAQHi Koji, See here for instructions on eudaq: http://yarr.readthedocs.io/en/eudaq/eudaq.html Swap into branch eudaq. Dont forget to program the correct firmware (assuming you already have the adapter board). Some remarks: - I had a merge conflict problem in the firmware and Im not 100% that is resolvers properly. If it is not right, YARR would not answer to triggers, which you should see if the RC does not see more trigger. - I had to change the way events get send to the RC, this is untested and I hope it works. - There is a version of the converter, but Im sure there were local changes and I cant get onto the eudaq machine at SLAC due to some stupid permissions. We need to wait until someone sends me the file. If you give me a not to random time window in your night where I can test some things with, we could do that. I have to run some errants and will not be at my laptop the whole time. Otherwise we can get everything running once Im there in person. Cheers, Timonhttps://eutelescope.web.cern.ch/forum/multiple-dut-events-tlu-trigger | |||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

| Changed: | |||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

| < < | instructions on eudaq ->

http://yarr.readthedocs.io/en/latest/eudaq.html | ||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

| > > | instructions on eudaq -> http://yarr.readthedocs.io/en/latest/eudaq.htmlExttrigger mode | ||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

| Added: | |||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

| > > |

Seabas firmware : MPPC bias : ~60V Latency : 70 ///// memo KEKFE65-13@-20degC CompVbnDac: 50 PrempVbpDac: 120 VbnLccDac : 200 VffDac : 15 | ||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

ImagesThere are 24 images in this page -- Log noteAfterIrrad20161018

| |||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

Revision 272017-06-17 - JunkiSuzuki

DAQ development for FE65-P2 chipIntroductionFE65-P2 is the readout ASIC with 65nm processing as pre-pre-production for the RD53A/B chips used by HL-LHC ITK pixel upgrade. more information is available in : motivation talk in AUW April 2016Chips and Bump Bonding at SLACsensor name,bias(type), condition, patch work, dose, | |||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

| Changed: | |||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

| < < |

| ||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

| > > |

| ||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

| |||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

| Changed: | |||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

| < < |

| ||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

| > > |

| ||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

DAQ development by SPEC

How to setup SPEC board

mkdir -p /home/atlasj/work/SPEC/YARR cd /home/atlasj/work/SPEC/YARR/ git clone https://github.com/Yarr/Yarr.git git fetch git checkout fe65_p2 cd /home/atlasj/work/SPEC/YARR/Yarr/src/kernel make sudo make install sudo depmod cd ../ ; make

sudo modprobe specDriver bin/programFpga ../hdl/syn/yarr_fe65p2_revB.bit bin/test bin/benchmarkDma How to configure chips and run scantuning

General scan consolHitOr self trigger scan1. Run digital scan2. Run analog scan 3. Prepare config: - Enable all pixels: # bin/config_fe65-p2 fe65p2.json (Overwrites config file) - Apply digital scan mask: # bin/applyMask fe65p2_ch0_digitalscan_EnMask.dat fe65p2.json - Copy masked config: # cp masked_fe65p2.json fe65p2.json - Apply analog scan mask: # bin/applyMask fe65p2_ch0_analogscan_EnMask.dat fe65p2.json - Copy masked config: # cp masked_fe65p2.json fe65p2.json 4. Run noise scan (~5min) 5. Apply noise mask: - Apply digital scan mask: # bin/applyMask fe65p2_ch0_noisescan_NoiseMask.dat fe65p2.json - Copy masked config: # cp masked_fe65p2.json fe65p2.json 6. Mask stuck/noise hitter pixels: - #bin/fixHitbus fe65p2.json (takes quite some time ~15min) - Only pixels which will get masked get printed to stdout, optimally these should not be many - If many pixels appear to not work something is wrong - You can observe the process by probing HitOr Output and Trigger, there should be two hitOr pulses per trigger - The program produces a mask hitbus_enMask.png - Copy masked config: # cp masked_fe65p2.json fe65p2.json 7. Run exttrigger scan: - If everything went right you should observe a trigger rate of a few Hz without a particle source - With source the rate should be much higher - The internal dead time is 200bc (currently hardcoded for testing) YARR DAQ in EUDAQHi Koji, See here for instructions on eudaq: http://yarr.readthedocs.io/en/eudaq/eudaq.html Swap into branch eudaq. Dont forget to program the correct firmware (assuming you already have the adapter board). Some remarks: - I had a merge conflict problem in the firmware and Im not 100% that is resolvers properly. If it is not right, YARR would not answer to triggers, which you should see if the RC does not see more trigger. - I had to change the way events get send to the RC, this is untested and I hope it works. - There is a version of the converter, but Im sure there were local changes and I cant get onto the eudaq machine at SLAC due to some stupid permissions. We need to wait until someone sends me the file. If you give me a not to random time window in your night where I can test some things with, we could do that. I have to run some errants and will not be at my laptop the whole time. Otherwise we can get everything running once Im there in person. Cheers, Timonhttps://eutelescope.web.cern.ch/forum/multiple-dut-events-tlu-trigger ImagesThere are 24 images in this page -- Log noteAfterIrrad20161018

| |||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

Revision 262017-06-17 - JunkiSuzuki

DAQ development for FE65-P2 chipIntroductionFE65-P2 is the readout ASIC with 65nm processing as pre-pre-production for the RD53A/B chips used by HL-LHC ITK pixel upgrade. more information is available in : motivation talk in AUW April 2016Chips and Bump Bonding at SLACsensor name,bias(type), condition, patch work, dose,

| |||||||||||||||||||||||||||||||||||||||||||||||||||||||||

| Changed: | |||||||||||||||||||||||||||||||||||||||||||||||||||||||||

| < < |

| ||||||||||||||||||||||||||||||||||||||||||||||||||||||||

| > > |

| ||||||||||||||||||||||||||||||||||||||||||||||||||||||||

| |||||||||||||||||||||||||||||||||||||||||||||||||||||||||

| Changed: | |||||||||||||||||||||||||||||||||||||||||||||||||||||||||

| < < |

| ||||||||||||||||||||||||||||||||||||||||||||||||||||||||

| > > |

| ||||||||||||||||||||||||||||||||||||||||||||||||||||||||

DAQ development by SPEC

How to setup SPEC board

mkdir -p /home/atlasj/work/SPEC/YARR cd /home/atlasj/work/SPEC/YARR/ git clone https://github.com/Yarr/Yarr.git git fetch git checkout fe65_p2 cd /home/atlasj/work/SPEC/YARR/Yarr/src/kernel make sudo make install sudo depmod cd ../ ; make

sudo modprobe specDriver bin/programFpga ../hdl/syn/yarr_fe65p2_revB.bit bin/test bin/benchmarkDma How to configure chips and run scantuning

General scan consolHitOr self trigger scan1. Run digital scan2. Run analog scan 3. Prepare config: - Enable all pixels: # bin/config_fe65-p2 fe65p2.json (Overwrites config file) - Apply digital scan mask: # bin/applyMask fe65p2_ch0_digitalscan_EnMask.dat fe65p2.json - Copy masked config: # cp masked_fe65p2.json fe65p2.json - Apply analog scan mask: # bin/applyMask fe65p2_ch0_analogscan_EnMask.dat fe65p2.json - Copy masked config: # cp masked_fe65p2.json fe65p2.json 4. Run noise scan (~5min) 5. Apply noise mask: - Apply digital scan mask: # bin/applyMask fe65p2_ch0_noisescan_NoiseMask.dat fe65p2.json - Copy masked config: # cp masked_fe65p2.json fe65p2.json 6. Mask stuck/noise hitter pixels: - #bin/fixHitbus fe65p2.json (takes quite some time ~15min) - Only pixels which will get masked get printed to stdout, optimally these should not be many - If many pixels appear to not work something is wrong - You can observe the process by probing HitOr Output and Trigger, there should be two hitOr pulses per trigger - The program produces a mask hitbus_enMask.png - Copy masked config: # cp masked_fe65p2.json fe65p2.json 7. Run exttrigger scan: - If everything went right you should observe a trigger rate of a few Hz without a particle source - With source the rate should be much higher - The internal dead time is 200bc (currently hardcoded for testing) YARR DAQ in EUDAQHi Koji, See here for instructions on eudaq: http://yarr.readthedocs.io/en/eudaq/eudaq.html Swap into branch eudaq. Dont forget to program the correct firmware (assuming you already have the adapter board). Some remarks: - I had a merge conflict problem in the firmware and Im not 100% that is resolvers properly. If it is not right, YARR would not answer to triggers, which you should see if the RC does not see more trigger. - I had to change the way events get send to the RC, this is untested and I hope it works. - There is a version of the converter, but Im sure there were local changes and I cant get onto the eudaq machine at SLAC due to some stupid permissions. We need to wait until someone sends me the file. If you give me a not to random time window in your night where I can test some things with, we could do that. I have to run some errants and will not be at my laptop the whole time. Otherwise we can get everything running once Im there in person. Cheers, Timonhttps://eutelescope.web.cern.ch/forum/multiple-dut-events-tlu-trigger ImagesThere are 24 images in this page -- Log noteAfterIrrad20161018

| |||||||||||||||||||||||||||||||||||||||||||||||||||||||||

Revision 252017-06-16 - JunkiSuzuki

DAQ development for FE65-P2 chipIntroductionFE65-P2 is the readout ASIC with 65nm processing as pre-pre-production for the RD53A/B chips used by HL-LHC ITK pixel upgrade. more information is available in : motivation talk in AUW April 2016Chips and Bump Bonding at SLACsensor name,bias(type), condition, patch work, dose, | |||||||||||||||||||||||||||||||||||||||||||||||||||

| Changed: | |||||||||||||||||||||||||||||||||||||||||||||||||||

| < < |

| ||||||||||||||||||||||||||||||||||||||||||||||||||

| > > |

| ||||||||||||||||||||||||||||||||||||||||||||||||||

| |||||||||||||||||||||||||||||||||||||||||||||||||||

| Changed: | |||||||||||||||||||||||||||||||||||||||||||||||||||

| < < |

| ||||||||||||||||||||||||||||||||||||||||||||||||||

| > > |

| ||||||||||||||||||||||||||||||||||||||||||||||||||

| |||||||||||||||||||||||||||||||||||||||||||||||||||

| Added: | |||||||||||||||||||||||||||||||||||||||||||||||||||

| > > |

| ||||||||||||||||||||||||||||||||||||||||||||||||||

DAQ development by SPEC

How to setup SPEC board

mkdir -p /home/atlasj/work/SPEC/YARR cd /home/atlasj/work/SPEC/YARR/ git clone https://github.com/Yarr/Yarr.git git fetch git checkout fe65_p2 cd /home/atlasj/work/SPEC/YARR/Yarr/src/kernel make sudo make install sudo depmod cd ../ ; make

sudo modprobe specDriver bin/programFpga ../hdl/syn/yarr_fe65p2_revB.bit bin/test bin/benchmarkDma How to configure chips and run scantuning

General scan consolHitOr self trigger scan1. Run digital scan2. Run analog scan 3. Prepare config: - Enable all pixels: # bin/config_fe65-p2 fe65p2.json (Overwrites config file) - Apply digital scan mask: # bin/applyMask fe65p2_ch0_digitalscan_EnMask.dat fe65p2.json - Copy masked config: # cp masked_fe65p2.json fe65p2.json - Apply analog scan mask: # bin/applyMask fe65p2_ch0_analogscan_EnMask.dat fe65p2.json - Copy masked config: # cp masked_fe65p2.json fe65p2.json 4. Run noise scan (~5min) 5. Apply noise mask: - Apply digital scan mask: # bin/applyMask fe65p2_ch0_noisescan_NoiseMask.dat fe65p2.json - Copy masked config: # cp masked_fe65p2.json fe65p2.json 6. Mask stuck/noise hitter pixels: - #bin/fixHitbus fe65p2.json (takes quite some time ~15min) - Only pixels which will get masked get printed to stdout, optimally these should not be many - If many pixels appear to not work something is wrong - You can observe the process by probing HitOr Output and Trigger, there should be two hitOr pulses per trigger - The program produces a mask hitbus_enMask.png - Copy masked config: # cp masked_fe65p2.json fe65p2.json 7. Run exttrigger scan: - If everything went right you should observe a trigger rate of a few Hz without a particle source - With source the rate should be much higher - The internal dead time is 200bc (currently hardcoded for testing) YARR DAQ in EUDAQHi Koji, See here for instructions on eudaq: http://yarr.readthedocs.io/en/eudaq/eudaq.html Swap into branch eudaq. Dont forget to program the correct firmware (assuming you already have the adapter board). Some remarks: - I had a merge conflict problem in the firmware and Im not 100% that is resolvers properly. If it is not right, YARR would not answer to triggers, which you should see if the RC does not see more trigger. - I had to change the way events get send to the RC, this is untested and I hope it works. - There is a version of the converter, but Im sure there were local changes and I cant get onto the eudaq machine at SLAC due to some stupid permissions. We need to wait until someone sends me the file. If you give me a not to random time window in your night where I can test some things with, we could do that. I have to run some errants and will not be at my laptop the whole time. Otherwise we can get everything running once Im there in person. Cheers, Timonhttps://eutelescope.web.cern.ch/forum/multiple-dut-events-tlu-trigger ImagesThere are 24 images in this page -- Log noteAfterIrrad20161018

| |||||||||||||||||||||||||||||||||||||||||||||||||||

Revision 242017-02-22 - AtlasjSilicon

DAQ development for FE65-P2 chipIntroductionFE65-P2 is the readout ASIC with 65nm processing as pre-pre-production for the RD53A/B chips used by HL-LHC ITK pixel upgrade. more information is available in : motivation talk in AUW April 2016Chips and Bump Bonding at SLACsensor name,bias(type), condition, patch work, dose,

| |||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

| Changed: | |||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

| < < |

| ||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

| > > |

| ||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

DAQ development by SPEC

How to setup SPEC board

mkdir -p /home/atlasj/work/SPEC/YARR cd /home/atlasj/work/SPEC/YARR/ git clone https://github.com/Yarr/Yarr.git git fetch git checkout fe65_p2 cd /home/atlasj/work/SPEC/YARR/Yarr/src/kernel make sudo make install sudo depmod cd ../ ; make

sudo modprobe specDriver bin/programFpga ../hdl/syn/yarr_fe65p2_revB.bit bin/test bin/benchmarkDma How to configure chips and run scantuning

General scan consolHitOr self trigger scan1. Run digital scan2. Run analog scan 3. Prepare config: - Enable all pixels: # bin/config_fe65-p2 fe65p2.json (Overwrites config file) - Apply digital scan mask: # bin/applyMask fe65p2_ch0_digitalscan_EnMask.dat fe65p2.json - Copy masked config: # cp masked_fe65p2.json fe65p2.json - Apply analog scan mask: # bin/applyMask fe65p2_ch0_analogscan_EnMask.dat fe65p2.json - Copy masked config: # cp masked_fe65p2.json fe65p2.json 4. Run noise scan (~5min) 5. Apply noise mask: - Apply digital scan mask: # bin/applyMask fe65p2_ch0_noisescan_NoiseMask.dat fe65p2.json - Copy masked config: # cp masked_fe65p2.json fe65p2.json 6. Mask stuck/noise hitter pixels: - #bin/fixHitbus fe65p2.json (takes quite some time ~15min) - Only pixels which will get masked get printed to stdout, optimally these should not be many - If many pixels appear to not work something is wrong - You can observe the process by probing HitOr Output and Trigger, there should be two hitOr pulses per trigger - The program produces a mask hitbus_enMask.png - Copy masked config: # cp masked_fe65p2.json fe65p2.json 7. Run exttrigger scan: - If everything went right you should observe a trigger rate of a few Hz without a particle source - With source the rate should be much higher - The internal dead time is 200bc (currently hardcoded for testing) YARR DAQ in EUDAQHi Koji, See here for instructions on eudaq: http://yarr.readthedocs.io/en/eudaq/eudaq.html Swap into branch eudaq. Dont forget to program the correct firmware (assuming you already have the adapter board). Some remarks: - I had a merge conflict problem in the firmware and Im not 100% that is resolvers properly. If it is not right, YARR would not answer to triggers, which you should see if the RC does not see more trigger. - I had to change the way events get send to the RC, this is untested and I hope it works. - There is a version of the converter, but Im sure there were local changes and I cant get onto the eudaq machine at SLAC due to some stupid permissions. We need to wait until someone sends me the file. If you give me a not to random time window in your night where I can test some things with, we could do that. I have to run some errants and will not be at my laptop the whole time. Otherwise we can get everything running once Im there in person. Cheers, Timonhttps://eutelescope.web.cern.ch/forum/multiple-dut-events-tlu-trigger | |||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

| Added: | |||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

| > > |

instructions on eudaq ->

http://yarr.readthedocs.io/en/latest/eudaq.html | ||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

ImagesThere are 24 images in this page -- Log noteAfterIrrad20161018

| |||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

Revision 232017-02-17 - AtlasjSilicon

DAQ development for FE65-P2 chipIntroductionFE65-P2 is the readout ASIC with 65nm processing as pre-pre-production for the RD53A/B chips used by HL-LHC ITK pixel upgrade. more information is available in : motivation talk in AUW April 2016Chips and Bump Bonding at SLACsensor name,bias(type), condition, patch work, dose,

| |||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

| Changed: | |||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

| < < |

| ||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

| > > |

| ||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

DAQ development by SPEC

How to setup SPEC board

mkdir -p /home/atlasj/work/SPEC/YARR cd /home/atlasj/work/SPEC/YARR/ git clone https://github.com/Yarr/Yarr.git git fetch git checkout fe65_p2 cd /home/atlasj/work/SPEC/YARR/Yarr/src/kernel make sudo make install sudo depmod cd ../ ; make

sudo modprobe specDriver bin/programFpga ../hdl/syn/yarr_fe65p2_revB.bit bin/test bin/benchmarkDma How to configure chips and run scantuning

General scan consolHitOr self trigger scan1. Run digital scan2. Run analog scan 3. Prepare config: - Enable all pixels: # bin/config_fe65-p2 fe65p2.json (Overwrites config file) - Apply digital scan mask: # bin/applyMask fe65p2_ch0_digitalscan_EnMask.dat fe65p2.json - Copy masked config: # cp masked_fe65p2.json fe65p2.json - Apply analog scan mask: # bin/applyMask fe65p2_ch0_analogscan_EnMask.dat fe65p2.json - Copy masked config: # cp masked_fe65p2.json fe65p2.json 4. Run noise scan (~5min) 5. Apply noise mask: - Apply digital scan mask: # bin/applyMask fe65p2_ch0_noisescan_NoiseMask.dat fe65p2.json - Copy masked config: # cp masked_fe65p2.json fe65p2.json 6. Mask stuck/noise hitter pixels: - #bin/fixHitbus fe65p2.json (takes quite some time ~15min) - Only pixels which will get masked get printed to stdout, optimally these should not be many - If many pixels appear to not work something is wrong - You can observe the process by probing HitOr Output and Trigger, there should be two hitOr pulses per trigger - The program produces a mask hitbus_enMask.png - Copy masked config: # cp masked_fe65p2.json fe65p2.json 7. Run exttrigger scan: - If everything went right you should observe a trigger rate of a few Hz without a particle source - With source the rate should be much higher - The internal dead time is 200bc (currently hardcoded for testing) YARR DAQ in EUDAQHi Koji, See here for instructions on eudaq: http://yarr.readthedocs.io/en/eudaq/eudaq.html Swap into branch eudaq. Dont forget to program the correct firmware (assuming you already have the adapter board). Some remarks: - I had a merge conflict problem in the firmware and Im not 100% that is resolvers properly. If it is not right, YARR would not answer to triggers, which you should see if the RC does not see more trigger. - I had to change the way events get send to the RC, this is untested and I hope it works. - There is a version of the converter, but Im sure there were local changes and I cant get onto the eudaq machine at SLAC due to some stupid permissions. We need to wait until someone sends me the file. If you give me a not to random time window in your night where I can test some things with, we could do that. I have to run some errants and will not be at my laptop the whole time. Otherwise we can get everything running once Im there in person. Cheers, Timonhttps://eutelescope.web.cern.ch/forum/multiple-dut-events-tlu-trigger ImagesThere are 24 images in this page -- Log noteAfterIrrad20161018

| |||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

Revision 222017-02-17 - AtlasjSilicon

DAQ development for FE65-P2 chipIntroductionFE65-P2 is the readout ASIC with 65nm processing as pre-pre-production for the RD53A/B chips used by HL-LHC ITK pixel upgrade. more information is available in : motivation talk in AUW April 2016Chips and Bump Bonding at SLACsensor name,bias(type), condition, patch work, dose,

| |||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

| Changed: | |||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

| < < | |||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

| > > |

| ||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

| Added: | |||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

| > > |

| ||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

DAQ development by SPEC

How to setup SPEC board

mkdir -p /home/atlasj/work/SPEC/YARR cd /home/atlasj/work/SPEC/YARR/ git clone https://github.com/Yarr/Yarr.git git fetch git checkout fe65_p2 cd /home/atlasj/work/SPEC/YARR/Yarr/src/kernel make sudo make install sudo depmod cd ../ ; make

sudo modprobe specDriver bin/programFpga ../hdl/syn/yarr_fe65p2_revB.bit bin/test bin/benchmarkDma How to configure chips and run scantuning

General scan consolHitOr self trigger scan1. Run digital scan2. Run analog scan 3. Prepare config: - Enable all pixels: # bin/config_fe65-p2 fe65p2.json (Overwrites config file) - Apply digital scan mask: # bin/applyMask fe65p2_ch0_digitalscan_EnMask.dat fe65p2.json - Copy masked config: # cp masked_fe65p2.json fe65p2.json - Apply analog scan mask: # bin/applyMask fe65p2_ch0_analogscan_EnMask.dat fe65p2.json - Copy masked config: # cp masked_fe65p2.json fe65p2.json 4. Run noise scan (~5min) 5. Apply noise mask: - Apply digital scan mask: # bin/applyMask fe65p2_ch0_noisescan_NoiseMask.dat fe65p2.json - Copy masked config: # cp masked_fe65p2.json fe65p2.json 6. Mask stuck/noise hitter pixels: - #bin/fixHitbus fe65p2.json (takes quite some time ~15min) - Only pixels which will get masked get printed to stdout, optimally these should not be many - If many pixels appear to not work something is wrong - You can observe the process by probing HitOr Output and Trigger, there should be two hitOr pulses per trigger - The program produces a mask hitbus_enMask.png - Copy masked config: # cp masked_fe65p2.json fe65p2.json 7. Run exttrigger scan: - If everything went right you should observe a trigger rate of a few Hz without a particle source - With source the rate should be much higher - The internal dead time is 200bc (currently hardcoded for testing) YARR DAQ in EUDAQHi Koji, See here for instructions on eudaq: http://yarr.readthedocs.io/en/eudaq/eudaq.html Swap into branch eudaq. Dont forget to program the correct firmware (assuming you already have the adapter board). Some remarks: - I had a merge conflict problem in the firmware and Im not 100% that is resolvers properly. If it is not right, YARR would not answer to triggers, which you should see if the RC does not see more trigger. - I had to change the way events get send to the RC, this is untested and I hope it works. - There is a version of the converter, but Im sure there were local changes and I cant get onto the eudaq machine at SLAC due to some stupid permissions. We need to wait until someone sends me the file. If you give me a not to random time window in your night where I can test some things with, we could do that. I have to run some errants and will not be at my laptop the whole time. Otherwise we can get everything running once Im there in person. Cheers, Timonhttps://eutelescope.web.cern.ch/forum/multiple-dut-events-tlu-trigger ImagesThere are 24 images in this page -- Log noteAfterIrrad20161018

| |||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

Revision 212017-02-04 - JunkiSuzuki

DAQ development for FE65-P2 chipIntroductionFE65-P2 is the readout ASIC with 65nm processing as pre-pre-production for the RD53A/B chips used by HL-LHC ITK pixel upgrade. more information is available in : motivation talk in AUW April 2016 | |||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

| Added: | |||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

| > > | FE65-P2.pdf | ||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

Chips and Bump Bonding at SLACsensor name,bias(type), condition, patch work, dose,

DAQ development by SPEC

How to setup SPEC board

mkdir -p /home/atlasj/work/SPEC/YARR cd /home/atlasj/work/SPEC/YARR/ git clone https://github.com/Yarr/Yarr.git git fetch git checkout fe65_p2 cd /home/atlasj/work/SPEC/YARR/Yarr/src/kernel make sudo make install sudo depmod cd ../ ; make

sudo modprobe specDriver bin/programFpga ../hdl/syn/yarr_fe65p2_revB.bit bin/test bin/benchmarkDma How to configure chips and run scantuning

General scan consolHitOr self trigger scan1. Run digital scan2. Run analog scan 3. Prepare config: - Enable all pixels: # bin/config_fe65-p2 fe65p2.json (Overwrites config file) - Apply digital scan mask: # bin/applyMask fe65p2_ch0_digitalscan_EnMask.dat fe65p2.json - Copy masked config: # cp masked_fe65p2.json fe65p2.json - Apply analog scan mask: # bin/applyMask fe65p2_ch0_analogscan_EnMask.dat fe65p2.json - Copy masked config: # cp masked_fe65p2.json fe65p2.json 4. Run noise scan (~5min) 5. Apply noise mask: - Apply digital scan mask: # bin/applyMask fe65p2_ch0_noisescan_NoiseMask.dat fe65p2.json - Copy masked config: # cp masked_fe65p2.json fe65p2.json 6. Mask stuck/noise hitter pixels: - #bin/fixHitbus fe65p2.json (takes quite some time ~15min) - Only pixels which will get masked get printed to stdout, optimally these should not be many - If many pixels appear to not work something is wrong - You can observe the process by probing HitOr Output and Trigger, there should be two hitOr pulses per trigger - The program produces a mask hitbus_enMask.png - Copy masked config: # cp masked_fe65p2.json fe65p2.json 7. Run exttrigger scan: - If everything went right you should observe a trigger rate of a few Hz without a particle source - With source the rate should be much higher - The internal dead time is 200bc (currently hardcoded for testing) YARR DAQ in EUDAQHi Koji, See here for instructions on eudaq: http://yarr.readthedocs.io/en/eudaq/eudaq.html Swap into branch eudaq. Dont forget to program the correct firmware (assuming you already have the adapter board). Some remarks: - I had a merge conflict problem in the firmware and Im not 100% that is resolvers properly. If it is not right, YARR would not answer to triggers, which you should see if the RC does not see more trigger. - I had to change the way events get send to the RC, this is untested and I hope it works. - There is a version of the converter, but Im sure there were local changes and I cant get onto the eudaq machine at SLAC due to some stupid permissions. We need to wait until someone sends me the file. If you give me a not to random time window in your night where I can test some things with, we could do that. I have to run some errants and will not be at my laptop the whole time. Otherwise we can get everything running once Im there in person. Cheers, Timonhttps://eutelescope.web.cern.ch/forum/multiple-dut-events-tlu-trigger ImagesThere are 24 images in this page -- Log noteAfterIrrad20161018

| |||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

| Added: | |||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

| > > |

| ||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

Revision 202017-02-03 - JunkiSuzuki

DAQ development for FE65-P2 chipIntroductionFE65-P2 is the readout ASIC with 65nm processing as pre-pre-production for the RD53A/B chips used by HL-LHC ITK pixel upgrade. more information is available in : motivation talk in AUW April 2016Chips and Bump Bonding at SLACsensor name,bias(type), condition, patch work, dose,

| |||||||||||||||||||||||||||||||||||||||||||||||||||||||

| Changed: | |||||||||||||||||||||||||||||||||||||||||||||||||||||||

| < < |

| ||||||||||||||||||||||||||||||||||||||||||||||||||||||

| > > |

| ||||||||||||||||||||||||||||||||||||||||||||||||||||||

DAQ development by SPEC

How to setup SPEC board

mkdir -p /home/atlasj/work/SPEC/YARR cd /home/atlasj/work/SPEC/YARR/ git clone https://github.com/Yarr/Yarr.git git fetch git checkout fe65_p2 cd /home/atlasj/work/SPEC/YARR/Yarr/src/kernel make sudo make install sudo depmod cd ../ ; make

sudo modprobe specDriver bin/programFpga ../hdl/syn/yarr_fe65p2_revB.bit bin/test bin/benchmarkDma How to configure chips and run scantuning

General scan consolHitOr self trigger scan1. Run digital scan2. Run analog scan 3. Prepare config: - Enable all pixels: # bin/config_fe65-p2 fe65p2.json (Overwrites config file) - Apply digital scan mask: # bin/applyMask fe65p2_ch0_digitalscan_EnMask.dat fe65p2.json - Copy masked config: # cp masked_fe65p2.json fe65p2.json - Apply analog scan mask: # bin/applyMask fe65p2_ch0_analogscan_EnMask.dat fe65p2.json - Copy masked config: # cp masked_fe65p2.json fe65p2.json 4. Run noise scan (~5min) 5. Apply noise mask: - Apply digital scan mask: # bin/applyMask fe65p2_ch0_noisescan_NoiseMask.dat fe65p2.json - Copy masked config: # cp masked_fe65p2.json fe65p2.json 6. Mask stuck/noise hitter pixels: - #bin/fixHitbus fe65p2.json (takes quite some time ~15min) - Only pixels which will get masked get printed to stdout, optimally these should not be many - If many pixels appear to not work something is wrong - You can observe the process by probing HitOr Output and Trigger, there should be two hitOr pulses per trigger - The program produces a mask hitbus_enMask.png - Copy masked config: # cp masked_fe65p2.json fe65p2.json 7. Run exttrigger scan: - If everything went right you should observe a trigger rate of a few Hz without a particle source - With source the rate should be much higher - The internal dead time is 200bc (currently hardcoded for testing) YARR DAQ in EUDAQHi Koji, See here for instructions on eudaq: http://yarr.readthedocs.io/en/eudaq/eudaq.html Swap into branch eudaq. Dont forget to program the correct firmware (assuming you already have the adapter board). Some remarks: - I had a merge conflict problem in the firmware and Im not 100% that is resolvers properly. If it is not right, YARR would not answer to triggers, which you should see if the RC does not see more trigger. - I had to change the way events get send to the RC, this is untested and I hope it works. - There is a version of the converter, but Im sure there were local changes and I cant get onto the eudaq machine at SLAC due to some stupid permissions. We need to wait until someone sends me the file. If you give me a not to random time window in your night where I can test some things with, we could do that. I have to run some errants and will not be at my laptop the whole time. Otherwise we can get everything running once Im there in person. Cheers, Timonhttps://eutelescope.web.cern.ch/forum/multiple-dut-events-tlu-trigger ImagesThere are 24 images in this page -- Log noteAfterIrrad20161018

| |||||||||||||||||||||||||||||||||||||||||||||||||||||||

Revision 192017-02-03 - JunkiSuzuki

DAQ development for FE65-P2 chipIntroductionFE65-P2 is the readout ASIC with 65nm processing as pre-pre-production for the RD53A/B chips used by HL-LHC ITK pixel upgrade. more information is available in : motivation talk in AUW April 2016Chips and Bump Bonding at SLACsensor name,bias(type), condition, patch work, dose,

| |||||||||||||||||||||||||||||||||||||||||||||||||||

| Changed: | |||||||||||||||||||||||||||||||||||||||||||||||||||

| < < |

| ||||||||||||||||||||||||||||||||||||||||||||||||||

| > > |

| ||||||||||||||||||||||||||||||||||||||||||||||||||

DAQ development by SPEC

How to setup SPEC board

mkdir -p /home/atlasj/work/SPEC/YARR cd /home/atlasj/work/SPEC/YARR/ git clone https://github.com/Yarr/Yarr.git git fetch git checkout fe65_p2 cd /home/atlasj/work/SPEC/YARR/Yarr/src/kernel make sudo make install sudo depmod cd ../ ; make

sudo modprobe specDriver bin/programFpga ../hdl/syn/yarr_fe65p2_revB.bit bin/test bin/benchmarkDma How to configure chips and run scantuning

General scan consolHitOr self trigger scan1. Run digital scan2. Run analog scan 3. Prepare config: - Enable all pixels: # bin/config_fe65-p2 fe65p2.json (Overwrites config file) - Apply digital scan mask: # bin/applyMask fe65p2_ch0_digitalscan_EnMask.dat fe65p2.json - Copy masked config: # cp masked_fe65p2.json fe65p2.json - Apply analog scan mask: # bin/applyMask fe65p2_ch0_analogscan_EnMask.dat fe65p2.json - Copy masked config: # cp masked_fe65p2.json fe65p2.json 4. Run noise scan (~5min) 5. Apply noise mask: - Apply digital scan mask: # bin/applyMask fe65p2_ch0_noisescan_NoiseMask.dat fe65p2.json - Copy masked config: # cp masked_fe65p2.json fe65p2.json 6. Mask stuck/noise hitter pixels: - #bin/fixHitbus fe65p2.json (takes quite some time ~15min) - Only pixels which will get masked get printed to stdout, optimally these should not be many - If many pixels appear to not work something is wrong - You can observe the process by probing HitOr Output and Trigger, there should be two hitOr pulses per trigger - The program produces a mask hitbus_enMask.png - Copy masked config: # cp masked_fe65p2.json fe65p2.json 7. Run exttrigger scan: - If everything went right you should observe a trigger rate of a few Hz without a particle source - With source the rate should be much higher - The internal dead time is 200bc (currently hardcoded for testing) YARR DAQ in EUDAQ | |||||||||||||||||||||||||||||||||||||||||||||||||||

| Deleted: | |||||||||||||||||||||||||||||||||||||||||||||||||||

| < < | |||||||||||||||||||||||||||||||||||||||||||||||||||

Hi Koji, See here for instructions on eudaq: http://yarr.readthedocs.io/en/eudaq/eudaq.html Swap into branch eudaq. Dont forget to program the correct firmware (assuming you already have the adapter board). Some remarks: - I had a merge conflict problem in the firmware and Im not 100% that is resolvers properly. If it is not right, YARR would not answer to triggers, which you should see if the RC does not see more trigger. - I had to change the way events get send to the RC, this is untested and I hope it works. - There is a version of the converter, but Im sure there were local changes and I cant get onto the eudaq machine at SLAC due to some stupid permissions. We need to wait until someone sends me the file. If you give me a not to random time window in your night where I can test some things with, we could do that. I have to run some errants and will not be at my laptop the whole time. Otherwise we can get everything running once Im there in person. Cheers, Timonhttps://eutelescope.web.cern.ch/forum/multiple-dut-events-tlu-trigger ImagesThere are 24 images in this page -- Log noteAfterIrrad20161018

| |||||||||||||||||||||||||||||||||||||||||||||||||||

Revision 182016-10-26 - KojiNakamura

DAQ development for FE65-P2 chipIntroductionFE65-P2 is the readout ASIC with 65nm processing as pre-pre-production for the RD53A/B chips used by HL-LHC ITK pixel upgrade. more information is available in : motivation talk in AUW April 2016Chips and Bump Bonding at SLACsensor name,bias(type), condition, patch work, dose,

DAQ development by SPEC

How to setup SPEC board

mkdir -p /home/atlasj/work/SPEC/YARR cd /home/atlasj/work/SPEC/YARR/ git clone https://github.com/Yarr/Yarr.git git fetch git checkout fe65_p2 cd /home/atlasj/work/SPEC/YARR/Yarr/src/kernel make sudo make install sudo depmod cd ../ ; make

sudo modprobe specDriver bin/programFpga ../hdl/syn/yarr_fe65p2_revB.bit bin/test bin/benchmarkDma How to configure chips and run scantuning

General scan consolHitOr self trigger scan1. Run digital scan2. Run analog scan 3. Prepare config: - Enable all pixels: # bin/config_fe65-p2 fe65p2.json (Overwrites config file) - Apply digital scan mask: # bin/applyMask fe65p2_ch0_digitalscan_EnMask.dat fe65p2.json - Copy masked config: # cp masked_fe65p2.json fe65p2.json - Apply analog scan mask: # bin/applyMask fe65p2_ch0_analogscan_EnMask.dat fe65p2.json - Copy masked config: # cp masked_fe65p2.json fe65p2.json 4. Run noise scan (~5min) 5. Apply noise mask: - Apply digital scan mask: # bin/applyMask fe65p2_ch0_noisescan_NoiseMask.dat fe65p2.json - Copy masked config: # cp masked_fe65p2.json fe65p2.json 6. Mask stuck/noise hitter pixels: - #bin/fixHitbus fe65p2.json (takes quite some time ~15min) - Only pixels which will get masked get printed to stdout, optimally these should not be many - If many pixels appear to not work something is wrong - You can observe the process by probing HitOr Output and Trigger, there should be two hitOr pulses per trigger - The program produces a mask hitbus_enMask.png - Copy masked config: # cp masked_fe65p2.json fe65p2.json 7. Run exttrigger scan: - If everything went right you should observe a trigger rate of a few Hz without a particle source - With source the rate should be much higher - The internal dead time is 200bc (currently hardcoded for testing) | |||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

| Added: | |||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

| > > | YARR DAQ in EUDAQHi Koji, See here for instructions on eudaq: http://yarr.readthedocs.io/en/eudaq/eudaq.html Swap into branch eudaq. Dont forget to program the correct firmware (assuming you already have the adapter board). Some remarks: - I had a merge conflict problem in the firmware and Im not 100% that is resolvers properly. If it is not right, YARR would not answer to triggers, which you should see if the RC does not see more trigger. - I had to change the way events get send to the RC, this is untested and I hope it works. - There is a version of the converter, but Im sure there were local changes and I cant get onto the eudaq machine at SLAC due to some stupid permissions. We need to wait until someone sends me the file. If you give me a not to random time window in your night where I can test some things with, we could do that. I have to run some errants and will not be at my laptop the whole time. Otherwise we can get everything running once Im there in person. Cheers, Timonhttps://eutelescope.web.cern.ch/forum/multiple-dut-events-tlu-trigger | ||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

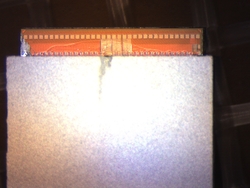

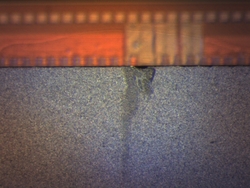

ImagesThere are 24 images in this page -- Log noteAfterIrrad20161018

| |||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

Revision 172016-10-20 - JunkiSuzuki

DAQ development for FE65-P2 chipIntroductionFE65-P2 is the readout ASIC with 65nm processing as pre-pre-production for the RD53A/B chips used by HL-LHC ITK pixel upgrade. more information is available in : motivation talk in AUW April 2016Chips and Bump Bonding at SLACsensor name,bias(type), condition, patch work, dose,

DAQ development by SPEC

How to setup SPEC board

mkdir -p /home/atlasj/work/SPEC/YARR cd /home/atlasj/work/SPEC/YARR/ git clone https://github.com/Yarr/Yarr.git git fetch git checkout fe65_p2 cd /home/atlasj/work/SPEC/YARR/Yarr/src/kernel make sudo make install sudo depmod cd ../ ; make

sudo modprobe specDriver bin/programFpga ../hdl/syn/yarr_fe65p2_revB.bit bin/test bin/benchmarkDma How to configure chips and run scantuning

General scan consolHitOr self trigger scan1. Run digital scan2. Run analog scan 3. Prepare config: - Enable all pixels: # bin/config_fe65-p2 fe65p2.json (Overwrites config file) - Apply digital scan mask: # bin/applyMask fe65p2_ch0_digitalscan_EnMask.dat fe65p2.json - Copy masked config: # cp masked_fe65p2.json fe65p2.json - Apply analog scan mask: # bin/applyMask fe65p2_ch0_analogscan_EnMask.dat fe65p2.json - Copy masked config: # cp masked_fe65p2.json fe65p2.json 4. Run noise scan (~5min) 5. Apply noise mask: - Apply digital scan mask: # bin/applyMask fe65p2_ch0_noisescan_NoiseMask.dat fe65p2.json - Copy masked config: # cp masked_fe65p2.json fe65p2.json 6. Mask stuck/noise hitter pixels: - #bin/fixHitbus fe65p2.json (takes quite some time ~15min) - Only pixels which will get masked get printed to stdout, optimally these should not be many - If many pixels appear to not work something is wrong - You can observe the process by probing HitOr Output and Trigger, there should be two hitOr pulses per trigger - The program produces a mask hitbus_enMask.png - Copy masked config: # cp masked_fe65p2.json fe65p2.json 7. Run exttrigger scan: - If everything went right you should observe a trigger rate of a few Hz without a particle source - With source the rate should be much higher - The internal dead time is 200bc (currently hardcoded for testing) ImagesThere are 24 images in this page -- Log noteAfterIrrad20161018

|

Revision 162016-10-19 - JunkiSuzuki

DAQ development for FE65-P2 chipIntroductionFE65-P2 is the readout ASIC with 65nm processing as pre-pre-production for the RD53A/B chips used by HL-LHC ITK pixel upgrade. more information is available in : motivation talk in AUW April 2016Chips and Bump Bonding at SLACsensor name,bias(type), condition, patch work, dose,

DAQ development by SPEC

How to setup SPEC board

mkdir -p /home/atlasj/work/SPEC/YARR cd /home/atlasj/work/SPEC/YARR/ git clone https://github.com/Yarr/Yarr.git git fetch git checkout fe65_p2 cd /home/atlasj/work/SPEC/YARR/Yarr/src/kernel make sudo make install sudo depmod cd ../ ; make

sudo modprobe specDriver bin/programFpga ../hdl/syn/yarr_fe65p2_revB.bit bin/test bin/benchmarkDma How to configure chips and run scantuning

General scan consolHitOr self trigger scan1. Run digital scan2. Run analog scan 3. Prepare config: - Enable all pixels: # bin/config_fe65-p2 fe65p2.json (Overwrites config file) - Apply digital scan mask: # bin/applyMask fe65p2_ch0_digitalscan_EnMask.dat fe65p2.json - Copy masked config: # cp masked_fe65p2.json fe65p2.json - Apply analog scan mask: # bin/applyMask fe65p2_ch0_analogscan_EnMask.dat fe65p2.json - Copy masked config: # cp masked_fe65p2.json fe65p2.json 4. Run noise scan (~5min) 5. Apply noise mask: - Apply digital scan mask: # bin/applyMask fe65p2_ch0_noisescan_NoiseMask.dat fe65p2.json - Copy masked config: # cp masked_fe65p2.json fe65p2.json 6. Mask stuck/noise hitter pixels: - #bin/fixHitbus fe65p2.json (takes quite some time ~15min) - Only pixels which will get masked get printed to stdout, optimally these should not be many - If many pixels appear to not work something is wrong - You can observe the process by probing HitOr Output and Trigger, there should be two hitOr pulses per trigger - The program produces a mask hitbus_enMask.png - Copy masked config: # cp masked_fe65p2.json fe65p2.json 7. Run exttrigger scan: - If everything went right you should observe a trigger rate of a few Hz without a particle source - With source the rate should be much higher - The internal dead time is 200bc (currently hardcoded for testing) ImagesThere are 24 images in this page -- | |||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

| Added: | |||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

| > > | Log noteAfterIrrad20161018 | ||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

| |||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

Revision 152016-10-18 - JunkiSuzuki

DAQ development for FE65-P2 chipIntroductionFE65-P2 is the readout ASIC with 65nm processing as pre-pre-production for the RD53A/B chips used by HL-LHC ITK pixel upgrade. more information is available in : motivation talk in AUW April 2016Chips and Bump Bonding at SLACsensor name,bias(type), condition, patch work, dose,

DAQ development by SPEC

How to setup SPEC board

mkdir -p /home/atlasj/work/SPEC/YARR cd /home/atlasj/work/SPEC/YARR/ git clone https://github.com/Yarr/Yarr.git git fetch git checkout fe65_p2 cd /home/atlasj/work/SPEC/YARR/Yarr/src/kernel make sudo make install sudo depmod cd ../ ; make

sudo modprobe specDriver bin/programFpga ../hdl/syn/yarr_fe65p2_revB.bit bin/test bin/benchmarkDma How to configure chips and run scantuning

| |||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

| Changed: | |||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

| < < |

| ||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

| > > |

| ||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

| Added: | |||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

| > > | ./bin/programFpga ../hdl/syn/yarr_fe65p2_revB.bit | ||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

General scan consolHitOr self trigger scan1. Run digital scan2. Run analog scan 3. Prepare config: - Enable all pixels: # bin/config_fe65-p2 fe65p2.json (Overwrites config file) - Apply digital scan mask: # bin/applyMask fe65p2_ch0_digitalscan_EnMask.dat fe65p2.json - Copy masked config: # cp masked_fe65p2.json fe65p2.json - Apply analog scan mask: # bin/applyMask fe65p2_ch0_analogscan_EnMask.dat fe65p2.json - Copy masked config: # cp masked_fe65p2.json fe65p2.json 4. Run noise scan (~5min) 5. Apply noise mask: - Apply digital scan mask: # bin/applyMask fe65p2_ch0_noisescan_NoiseMask.dat fe65p2.json - Copy masked config: # cp masked_fe65p2.json fe65p2.json 6. Mask stuck/noise hitter pixels: - #bin/fixHitbus fe65p2.json (takes quite some time ~15min) - Only pixels which will get masked get printed to stdout, optimally these should not be many - If many pixels appear to not work something is wrong - You can observe the process by probing HitOr Output and Trigger, there should be two hitOr pulses per trigger - The program produces a mask hitbus_enMask.png - Copy masked config: # cp masked_fe65p2.json fe65p2.json 7. Run exttrigger scan: - If everything went right you should observe a trigger rate of a few Hz without a particle source - With source the rate should be much higher - The internal dead time is 200bc (currently hardcoded for testing) ImagesThere are 24 images in this page --

| |||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

Revision 142016-10-13 - AtlasjSilicon

DAQ development for FE65-P2 chipIntroductionFE65-P2 is the readout ASIC with 65nm processing as pre-pre-production for the RD53A/B chips used by HL-LHC ITK pixel upgrade. more information is available in : motivation talk in AUW April 2016Chips and Bump Bonding at SLACsensor name,bias(type), condition, patch work, dose,

DAQ development by SPEC

How to setup SPEC board

mkdir -p /home/atlasj/work/SPEC/YARR cd /home/atlasj/work/SPEC/YARR/ git clone https://github.com/Yarr/Yarr.git git fetch git checkout fe65_p2 cd /home/atlasj/work/SPEC/YARR/Yarr/src/kernel make sudo make install sudo depmod cd ../ ; make | |||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

| Changed: | |||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

| < < |

| ||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

| > > |

| ||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

sudo modprobe specDriver bin/programFpga ../hdl/syn/yarr_fe65p2_revB.bit bin/test | |||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

| Deleted: | |||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

| < < | |||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

bin/benchmarkDma

How to configure chips and run scantuning

General scan consolHitOr self trigger scan1. Run digital scan2. Run analog scan 3. Prepare config: - Enable all pixels: # bin/config_fe65-p2 fe65p2.json (Overwrites config file) - Apply digital scan mask: # bin/applyMask fe65p2_ch0_digitalscan_EnMask.dat fe65p2.json - Copy masked config: # cp masked_fe65p2.json fe65p2.json - Apply analog scan mask: # bin/applyMask fe65p2_ch0_analogscan_EnMask.dat fe65p2.json - Copy masked config: # cp masked_fe65p2.json fe65p2.json 4. Run noise scan (~5min) 5. Apply noise mask: - Apply digital scan mask: # bin/applyMask fe65p2_ch0_noisescan_NoiseMask.dat fe65p2.json - Copy masked config: # cp masked_fe65p2.json fe65p2.json 6. Mask stuck/noise hitter pixels: - #bin/fixHitbus fe65p2.json (takes quite some time ~15min) - Only pixels which will get masked get printed to stdout, optimally these should not be many - If many pixels appear to not work something is wrong - You can observe the process by probing HitOr Output and Trigger, there should be two hitOr pulses per trigger - The program produces a mask hitbus_enMask.png - Copy masked config: # cp masked_fe65p2.json fe65p2.json 7. Run exttrigger scan: - If everything went right you should observe a trigger rate of a few Hz without a particle source - With source the rate should be much higher - The internal dead time is 200bc (currently hardcoded for testing) ImagesThere are 24 images in this page --

| |||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

Revision 132016-10-07 - AtlasjSilicon

DAQ development for FE65-P2 chipIntroductionFE65-P2 is the readout ASIC with 65nm processing as pre-pre-production for the RD53A/B chips used by HL-LHC ITK pixel upgrade. more information is available in : motivation talk in AUW April 2016Chips and Bump Bonding at SLACsensor name,bias(type), condition, patch work, dose,

| |||||||||||||||||||||||||||||||||||||||||||||||||||||||

| Changed: | |||||||||||||||||||||||||||||||||||||||||||||||||||||||

| < < |

| ||||||||||||||||||||||||||||||||||||||||||||||||||||||

| > > |

| ||||||||||||||||||||||||||||||||||||||||||||||||||||||

DAQ development by SPEC

How to setup SPEC board

mkdir -p /home/atlasj/work/SPEC/YARR cd /home/atlasj/work/SPEC/YARR/ git clone https://github.com/Yarr/Yarr.git git fetch git checkout fe65_p2 cd /home/atlasj/work/SPEC/YARR/Yarr/src/kernel make sudo make install sudo depmod cd ../ ; make

sudo modprobe specDriver bin/programFpga ../hdl/syn/yarr_fe65p2_revB.bit bin/test bin/benchmarkDma How to configure chips and run scantuning

General scan consolHitOr self trigger scan1. Run digital scan2. Run analog scan 3. Prepare config: - Enable all pixels: # bin/config_fe65-p2 fe65p2.json (Overwrites config file) - Apply digital scan mask: # bin/applyMask fe65p2_ch0_digitalscan_EnMask.dat fe65p2.json - Copy masked config: # cp masked_fe65p2.json fe65p2.json - Apply analog scan mask: # bin/applyMask fe65p2_ch0_analogscan_EnMask.dat fe65p2.json - Copy masked config: # cp masked_fe65p2.json fe65p2.json 4. Run noise scan (~5min) 5. Apply noise mask: - Apply digital scan mask: # bin/applyMask fe65p2_ch0_noisescan_NoiseMask.dat fe65p2.json - Copy masked config: # cp masked_fe65p2.json fe65p2.json 6. Mask stuck/noise hitter pixels: - #bin/fixHitbus fe65p2.json (takes quite some time ~15min) - Only pixels which will get masked get printed to stdout, optimally these should not be many - If many pixels appear to not work something is wrong - You can observe the process by probing HitOr Output and Trigger, there should be two hitOr pulses per trigger - The program produces a mask hitbus_enMask.png - Copy masked config: # cp masked_fe65p2.json fe65p2.json 7. Run exttrigger scan: - If everything went right you should observe a trigger rate of a few Hz without a particle source - With source the rate should be much higher - The internal dead time is 200bc (currently hardcoded for testing) ImagesThere are 24 images in this page --

| |||||||||||||||||||||||||||||||||||||||||||||||||||||||

Revision 122016-10-06 - AtlasjSilicon

DAQ development for FE65-P2 chipIntroductionFE65-P2 is the readout ASIC with 65nm processing as pre-pre-production for the RD53A/B chips used by HL-LHC ITK pixel upgrade. more information is available in : motivation talk in AUW April 2016Chips and Bump Bonding at SLACsensor name,bias(type), condition, patch work, dose,

| |||||||||||||||||||||||||||||||||||||||||||||||||

| Changed: | |||||||||||||||||||||||||||||||||||||||||||||||||

| < < |

| ||||||||||||||||||||||||||||||||||||||||||||||||

| > > |

| ||||||||||||||||||||||||||||||||||||||||||||||||

DAQ development by SPEC

How to setup SPEC board

mkdir -p /home/atlasj/work/SPEC/YARR cd /home/atlasj/work/SPEC/YARR/ git clone https://github.com/Yarr/Yarr.git git fetch git checkout fe65_p2 cd /home/atlasj/work/SPEC/YARR/Yarr/src/kernel make sudo make install sudo depmod cd ../ ; make

sudo modprobe specDriver bin/programFpga ../hdl/syn/yarr_fe65p2_revB.bit bin/test bin/benchmarkDma How to configure chips and run scantuning

| |||||||||||||||||||||||||||||||||||||||||||||||||

| Added: | |||||||||||||||||||||||||||||||||||||||||||||||||

| > > |

| ||||||||||||||||||||||||||||||||||||||||||||||||

General scan consolHitOr self trigger scan1. Run digital scan2. Run analog scan 3. Prepare config: - Enable all pixels: # bin/config_fe65-p2 fe65p2.json (Overwrites config file) - Apply digital scan mask: # bin/applyMask fe65p2_ch0_digitalscan_EnMask.dat fe65p2.json - Copy masked config: # cp masked_fe65p2.json fe65p2.json - Apply analog scan mask: # bin/applyMask fe65p2_ch0_analogscan_EnMask.dat fe65p2.json - Copy masked config: # cp masked_fe65p2.json fe65p2.json 4. Run noise scan (~5min) 5. Apply noise mask: - Apply digital scan mask: # bin/applyMask fe65p2_ch0_noisescan_NoiseMask.dat fe65p2.json - Copy masked config: # cp masked_fe65p2.json fe65p2.json 6. Mask stuck/noise hitter pixels: - #bin/fixHitbus fe65p2.json (takes quite some time ~15min) - Only pixels which will get masked get printed to stdout, optimally these should not be many - If many pixels appear to not work something is wrong - You can observe the process by probing HitOr Output and Trigger, there should be two hitOr pulses per trigger - The program produces a mask hitbus_enMask.png - Copy masked config: # cp masked_fe65p2.json fe65p2.json 7. Run exttrigger scan: - If everything went right you should observe a trigger rate of a few Hz without a particle source - With source the rate should be much higher - The internal dead time is 200bc (currently hardcoded for testing) ImagesThere are 24 images in this page --

| |||||||||||||||||||||||||||||||||||||||||||||||||

Revision 112016-10-06 - JunkiSuzuki

DAQ development for FE65-P2 chipIntroductionFE65-P2 is the readout ASIC with 65nm processing as pre-pre-production for the RD53A/B chips used by HL-LHC ITK pixel upgrade. more information is available in : motivation talk in AUW April 2016Chips and Bump Bonding at SLAC | |||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

| Changed: | |||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

| < < | KEKFE1 KEKFE2 KEKFE3 KEKFE4 KEKFE5 KEKFE6 | ||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

| > > | sensor name,bias(type), condition, patch work, dose,

| ||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

| Added: | |||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

| > > | |||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

DAQ development by SPEC

How to setup SPEC board

mkdir -p /home/atlasj/work/SPEC/YARR cd /home/atlasj/work/SPEC/YARR/ git clone https://github.com/Yarr/Yarr.git git fetch git checkout fe65_p2 cd /home/atlasj/work/SPEC/YARR/Yarr/src/kernel make sudo make install sudo depmod cd ../ ; make

sudo modprobe specDriver bin/programFpga ../hdl/syn/yarr_fe65p2_revB.bit bin/test bin/benchmarkDma How to configure chips and run scantuning

| |||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

| Changed: | |||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

| < < |

| ||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

| > > |

| ||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

General scan consolHitOr self trigger scan1. Run digital scan2. Run analog scan 3. Prepare config: - Enable all pixels: # bin/config_fe65-p2 fe65p2.json (Overwrites config file) - Apply digital scan mask: # bin/applyMask fe65p2_ch0_digitalscan_EnMask.dat fe65p2.json - Copy masked config: # cp masked_fe65p2.json fe65p2.json - Apply analog scan mask: # bin/applyMask fe65p2_ch0_analogscan_EnMask.dat fe65p2.json - Copy masked config: # cp masked_fe65p2.json fe65p2.json 4. Run noise scan (~5min) 5. Apply noise mask: - Apply digital scan mask: # bin/applyMask fe65p2_ch0_noisescan_NoiseMask.dat fe65p2.json - Copy masked config: # cp masked_fe65p2.json fe65p2.json 6. Mask stuck/noise hitter pixels: - #bin/fixHitbus fe65p2.json (takes quite some time ~15min) - Only pixels which will get masked get printed to stdout, optimally these should not be many - If many pixels appear to not work something is wrong - You can observe the process by probing HitOr Output and Trigger, there should be two hitOr pulses per trigger - The program produces a mask hitbus_enMask.png - Copy masked config: # cp masked_fe65p2.json fe65p2.json 7. Run exttrigger scan: - If everything went right you should observe a trigger rate of a few Hz without a particle source - With source the rate should be much higher - The internal dead time is 200bc (currently hardcoded for testing) ImagesThere are 24 images in this page --

| |||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

Revision 102016-10-03 - JunkiSuzuki

DAQ development for FE65-P2 chip | |||||||||||||||||||||||||||||||||||||||||||||||||

| Changed: | |||||||||||||||||||||||||||||||||||||||||||||||||

| < < | |||||||||||||||||||||||||||||||||||||||||||||||||

| > > | |||||||||||||||||||||||||||||||||||||||||||||||||

IntroductionFE65-P2 is the readout ASIC with 65nm processing as pre-pre-production for the RD53A/B chips used by HL-LHC ITK pixel upgrade. more information is available in : motivation talk in AUW April 2016Chips and Bump Bonding at SLACKEKFE1 KEKFE2 KEKFE3 KEKFE4 KEKFE5 KEKFE6DAQ development by SPEC

How to setup SPEC board

mkdir -p /home/atlasj/work/SPEC/YARR cd /home/atlasj/work/SPEC/YARR/ git clone https://github.com/Yarr/Yarr.git git fetch git checkout fe65_p2 cd /home/atlasj/work/SPEC/YARR/Yarr/src/kernel make sudo make install sudo depmod cd ../ ; make

sudo modprobe specDriver bin/programFpga ../hdl/syn/yarr_fe65p2_revB.bit bin/test bin/benchmarkDma How to configure chips and run scan | |||||||||||||||||||||||||||||||||||||||||||||||||

| Added: | |||||||||||||||||||||||||||||||||||||||||||||||||

| > > | tuning

| ||||||||||||||||||||||||||||||||||||||||||||||||

General scan consolHitOr self trigger scan1. Run digital scan2. Run analog scan 3. Prepare config: - Enable all pixels: # bin/config_fe65-p2 fe65p2.json (Overwrites config file) - Apply digital scan mask: # bin/applyMask fe65p2_ch0_digitalscan_EnMask.dat fe65p2.json - Copy masked config: # cp masked_fe65p2.json fe65p2.json - Apply analog scan mask: # bin/applyMask fe65p2_ch0_analogscan_EnMask.dat fe65p2.json - Copy masked config: # cp masked_fe65p2.json fe65p2.json 4. Run noise scan (~5min) 5. Apply noise mask: - Apply digital scan mask: # bin/applyMask fe65p2_ch0_noisescan_NoiseMask.dat fe65p2.json - Copy masked config: # cp masked_fe65p2.json fe65p2.json 6. Mask stuck/noise hitter pixels: - #bin/fixHitbus fe65p2.json (takes quite some time ~15min) - Only pixels which will get masked get printed to stdout, optimally these should not be many - If many pixels appear to not work something is wrong - You can observe the process by probing HitOr Output and Trigger, there should be two hitOr pulses per trigger - The program produces a mask hitbus_enMask.png - Copy masked config: # cp masked_fe65p2.json fe65p2.json 7. Run exttrigger scan: - If everything went right you should observe a trigger rate of a few Hz without a particle source - With source the rate should be much higher - The internal dead time is 200bc (currently hardcoded for testing) Images | |||||||||||||||||||||||||||||||||||||||||||||||||

| Changed: | |||||||||||||||||||||||||||||||||||||||||||||||||

| < < | There are 24 images in this page | ||||||||||||||||||||||||||||||||||||||||||||||||

| > > | There are 24 images in this page | ||||||||||||||||||||||||||||||||||||||||||||||||

--

| |||||||||||||||||||||||||||||||||||||||||||||||||

Revision 92016-08-23 - KojiNakamura

DAQ development for FE65-P2 chipIntroduction | |||||||||||||||||||||||||||||||||||||||||||||||||

| Changed: | |||||||||||||||||||||||||||||||||||||||||||||||||

| < < | FE65-P2 is the readout ASIC with 65nm processing as pre-pre-production for the RD53A /B chips used by HL-LHC ITK pixel upgrade. | ||||||||||||||||||||||||||||||||||||||||||||||||

| > > | FE65-P2 is the readout ASIC with 65nm processing as pre-pre-production for the RD53A/B chips used by HL-LHC ITK pixel upgrade. | ||||||||||||||||||||||||||||||||||||||||||||||||

|

more information is available in :

motivation talk in AUW April 2016 | |||||||||||||||||||||||||||||||||||||||||||||||||

| Changed: | |||||||||||||||||||||||||||||||||||||||||||||||||

| < < | Bump Bonding at SLAC | ||||||||||||||||||||||||||||||||||||||||||||||||

| > > | Chips and Bump Bonding at SLAC | ||||||||||||||||||||||||||||||||||||||||||||||||

| Added: | |||||||||||||||||||||||||||||||||||||||||||||||||

| > > | KEKFE1 KEKFE2 KEKFE3 KEKFE4 KEKFE5 KEKFE6 | ||||||||||||||||||||||||||||||||||||||||||||||||

DAQ development by SPEC

| |||||||||||||||||||||||||||||||||||||||||||||||||

| Changed: | |||||||||||||||||||||||||||||||||||||||||||||||||

| < < | How to setup SPEC board | ||||||||||||||||||||||||||||||||||||||||||||||||

| > > | How to setup SPEC board | ||||||||||||||||||||||||||||||||||||||||||||||||

mkdir -p /home/atlasj/work/SPEC/YARR cd /home/atlasj/work/SPEC/YARR/ git clone https://github.com/Yarr/Yarr.git git fetch git checkout fe65_p2 cd /home/atlasj/work/SPEC/YARR/Yarr/src/kernel make sudo make install sudo depmod cd ../ ; make

sudo modprobe specDriver bin/programFpga ../hdl/syn/yarr_fe65p2_revB.bit bin/test bin/benchmarkDma | |||||||||||||||||||||||||||||||||||||||||||||||||

| Added: | |||||||||||||||||||||||||||||||||||||||||||||||||

| > > | How to configure chips and run scanGeneral scan consolHitOr self trigger scan1. Run digital scan2. Run analog scan 3. Prepare config: - Enable all pixels: # bin/config_fe65-p2 fe65p2.json (Overwrites config file) - Apply digital scan mask: # bin/applyMask fe65p2_ch0_digitalscan_EnMask.dat fe65p2.json - Copy masked config: # cp masked_fe65p2.json fe65p2.json - Apply analog scan mask: # bin/applyMask fe65p2_ch0_analogscan_EnMask.dat fe65p2.json - Copy masked config: # cp masked_fe65p2.json fe65p2.json 4. Run noise scan (~5min) 5. Apply noise mask: - Apply digital scan mask: # bin/applyMask fe65p2_ch0_noisescan_NoiseMask.dat fe65p2.json - Copy masked config: # cp masked_fe65p2.json fe65p2.json 6. Mask stuck/noise hitter pixels: - #bin/fixHitbus fe65p2.json (takes quite some time ~15min) - Only pixels which will get masked get printed to stdout, optimally these should not be many - If many pixels appear to not work something is wrong - You can observe the process by probing HitOr Output and Trigger, there should be two hitOr pulses per trigger - The program produces a mask hitbus_enMask.png - Copy masked config: # cp masked_fe65p2.json fe65p2.json 7. Run exttrigger scan: - If everything went right you should observe a trigger rate of a few Hz without a particle source - With source the rate should be much higher - The internal dead time is 200bc (currently hardcoded for testing) | ||||||||||||||||||||||||||||||||||||||||||||||||

ImagesThere are 24 images in this page --

| |||||||||||||||||||||||||||||||||||||||||||||||||

Revision 82016-06-27 - KojiNakamura

DAQ development for FE65-P2 chipIntroductionFE65-P2 is the readout ASIC with 65nm processing as pre-pre-production for the RD53A /B chips used by HL-LHC ITK pixel upgrade. more information is available in : motivation talk in AUW April 2016Bump Bonding at SLACDAQ development by SPEC

How to setup SPEC board

mkdir -p /home/atlasj/work/SPEC/YARR cd /home/atlasj/work/SPEC/YARR/ git clone https://github.com/Yarr/Yarr.git git fetch git checkout fe65_p2 cd /home/atlasj/work/SPEC/YARR/Yarr/src/kernel make sudo make install sudo depmod cd ../ ; make

sudo modprobe specDriver bin/programFpga ../hdl/syn/yarr_fe65p2_revB.bit bin/test bin/benchmarkDma ImagesThere are 24 images in this page --

| |||||||||||||||||||||||||||||||||||||||||||

| Added: | |||||||||||||||||||||||||||||||||||||||||||

| > > |

| ||||||||||||||||||||||||||||||||||||||||||

Revision 72016-06-25 - KojiNakamura

DAQ development for FE65-P2 chipIntroductionFE65-P2 is the readout ASIC with 65nm processing as pre-pre-production for the RD53A /B chips used by HL-LHC ITK pixel upgrade. more information is available in : motivation talk in AUW April 2016Bump Bonding at SLACDAQ development by SPEC

| |||||||||||||||||||||||||||||||||||||||||

| Added: | |||||||||||||||||||||||||||||||||||||||||

| > > | How to setup SPEC board

mkdir -p /home/atlasj/work/SPEC/YARR cd /home/atlasj/work/SPEC/YARR/ git clone https://github.com/Yarr/Yarr.git git fetch git checkout fe65_p2 cd /home/atlasj/work/SPEC/YARR/Yarr/src/kernel make sudo make install sudo depmod cd ../ ; make | ||||||||||||||||||||||||||||||||||||||||

| Added: | |||||||||||||||||||||||||||||||||||||||||

| > > |

sudo modprobe specDriver bin/programFpga ../hdl/syn/yarr_fe65p2_revB.bit bin/test bin/benchmarkDma | ||||||||||||||||||||||||||||||||||||||||

Images | |||||||||||||||||||||||||||||||||||||||||

| Changed: | |||||||||||||||||||||||||||||||||||||||||

| < < |

There are 24 images in this page | ||||||||||||||||||||||||||||||||||||||||

| > > | |||||||||||||||||||||||||||||||||||||||||

| Added: | |||||||||||||||||||||||||||||||||||||||||

| > > | There are 24 images in this page | ||||||||||||||||||||||||||||||||||||||||

--