TLUfirmware

TLUadapter board

TLUadapter board(旧)-> 表、-> 裏 設計ミスでSEABASのJ1とJ3どちらか片方にしか接続できない問題(新しいものでは解決済み) Kyocera connector側:NIMinが回路図と反対側に繋がっていた->不幸なことにJ3 connectorであり、SEABAS上での接続先がADCだった(FPGAとは繋がっていなかった) Integration testではJ3に接続するつもりだったconnectorをSEABAS側J2に接続する(J1は未接続、JTAGが干渉してadapter boardはしっかりとは刺さっていない) SEABASのFPGAではLVDS信号は扱えない?(ucfファイルで指定しようとすると怒られる) 波形が出ない場合はPINの配置が間違っていないか確認する ->基本的にucfファイルを編集する。一覧で見たい場合はPlanAheadを起動する| 接続 | 信号名 | silk | in/out | signal | J2 | FPGA | notes |

|---|---|---|---|---|---|---|---|

| NIMin4 | NIMin[4] | in | NIM | D79 | N2 | ||

| NIMin5 | NIMin[5] | in | NIM | D78 | N1 | not implemented | |

| NIMin6 | NIMin[6] | in | NIM | D77 | P1 | not implemented | |

| NIMin7 | NIMin[7] | in | NIM | D76 | P3 | not implemented | |

| NIMout2 | NIMout[2] | NIMout3 | out | NIM | D74 | P5 | |

| NIMout3 | NIMout[3] | NIMout2 | out | NIM | D75 | P4 | |

| NIMout4 | NIMout[4] | NIMout? | out | NIM | D72 | R2 | |

| NIMout5 | NIMout[5] | NIMout4 | out | NIM | D73 | R1 | |

| dout0_p | dout0[0] | MPPC1_1 | in | (LVDS) | D52 | L3 | not implemented |

| dout0_n | dout0[1] | in | (LVDS) | D53 | L2 | ||

| dout_cmos0 | in | (TTL) | D54 | M5 | |||

| DAC_LDACn0 | out | D55 | M4 | ||||

| dout1_p | dout1[0] | MPPC2_1 | in | (LVDS) | D44 | J3 | |

| dout1_n | dout1[1] | in | (LVDS) | D45 | J1 | ||

| dout_cmos1 | in | (TTL) | D46 | K5 | |||

| DAC_LDACn1 | out | D47 | K3 | ||||

| DAC_PREn1 | out | D48 | K2 | ||||

| DAC_FS1 | out | D49 | K1 | ||||

| DAC_DIN1 | out | D50 | L5 | ||||

| DAC_SCLK1 | out | D51 | L4 | ||||

| dout2_p | dout2[0] | MPPC2 | in | (LVDS) | D63 | U4 | not implemented |

| dout2_n | dout2[1] | in | (LVDS) | D62 | U5 | ||

| dout_cmos2 | in | (TTL) | D61 | V1 | |||

| DAC_LDACn2 | out | D60 | V2 | ||||

| DAC_PREn2 | out | D40 | H2 | ||||

| DAC_FS2 | out | D41 | H1 | ||||

| DAC_DIN2 | out | D42 | J5 | ||||

| DAC_SCLK2 | out | D43 | J4 | ||||

| dout3_p | dout3[0] | MPPC3 | in | (LVDS) | D71 | R3 | not implemented |

| dout3_n | dout3[1] | in | (LVDS) | D70 | R5 | ||

| dout_cmos3 | in | (TTL) | D69 | T2 | |||

| DAC_LDACn3 | out | D68 | T3 | ||||

| DAC_PREn3 | out | D67 | T4 | ||||

| DAC_FS3 | out | D66 | T5 | ||||

| DAC_DIN3 | out | D65 | U1 | ||||

| DAC_SCLK3 | out | D64 | U2 | ||||

| ADC_P14 | LVCMOSin[0] | CMOSin6 | in | D56 | M2 | special connection for CMOSin HSIO2 busy |

|

| ADC_N14 | LVCMOSout[0] | CMOSout0 | out | D57 | M1 | special connection for CMOSout HSIO2 exttrigger |

| 接続 | 信号名 | silk | in/out | J1 | FPGA | 信号名 | 信号名 | silk | in/out | J3 | FPGA | ||

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| CMOSin0 | LVCMOSin[0] | in | D0 | E10 | NIMin4 | NIMin[4] | in | D99 | AC2 | ||||

| CMOSin1 | LVCMOSin[1] | in | D1 | A8 | NIMin5 | NIMin[5] | in | D98 | AC1 | ||||

| CMOSin2 | LVCMOSin[2] | in | D2 | C8 | NIMin6 | NIMin[6] | in | D97 | AB5 | ||||

| CMOSin3 | LVCMOSin[3] | in | D3 | D8 | NIMin7 | NIMin[7] | in | D96 | AB4 | ||||

| CMOSin4 | LVCMOSin[4] | in | D4 | A7 | NIMout2 | NIMout[2] | NIMout3 | out | D115 | AC3 | |||

| CMOSin5 | LVCMOSin[5] | in | D5 | B7 | NIMout3 | NIMout[3] | NIMout2 | out | D114 | AC4 | |||

| CMOSin6 | LVCMOSin[6] | in | D6 | C7 | NIMout4 | NIMout[4] | NIMout? | out | D113 | AD1 | |||

| CMOSout0 | LVCMOSout[0] | out | D7 | B6 | NIMout5 | NIMout[5] | NIMout4 | out | D112 | AD3 | |||

| CMOSout1 | LVCMOSout[1] | out | D8 | C6 | dout0_p | dout0[0] | MPPC1_1 | in | D92 | AA4 | |||

| CMOSout2 | LVCMOSout[2] | out | D9 | D6 | dout0_n | dout0[1] | in | D93 | AA5 | ||||

| CMOSout3 | LVCMOSout[3] | out | D10 | A5 | dout_cmos0 | in | D94 | AB1 | |||||

| CMOSout4 | LVCMOSout[4] | out | D11 | B5 | DAC_LDACn0 | out | D95 | AB2 | |||||

| CMOSout5 | LVCMOSout[5] | out | D12 | D5 | dout1_p | dout1[0] | MPPC2_1 | in | D84 | W4 | |||

| CMOSout6 | LVCMOSout[6] | out | D13 | A4 | dout1_n | dout1[1] | in | D85 | W5 | ||||

| CMOSout7 | LVCMOSout[7] | out | D14 | B4 | dout_cmos1 | in | D86 | Y1 | |||||

| CMOSout8 | LVCMOSout[8] | out | D15 | C4 | DAC_LDACn1 | out | D87 | Y2 | |||||

| LVDS1in | LVDSin[0] | LVDS | in | D23 | G2 | DAC_PREn1 | out | D88 | Y3 | ||||

| LVDS2out | LVDSout[0] | out | D22 | G1 | DAC_FS1 | out | D89 | Y5 | |||||

| LVDS3in | LVDSin[1] | in | D21 | H4 | DAC_DIN1 | out | D90 | AA2 | |||||

| LVDS4out | LVDSout[1] | out | D20 | H3 | DAC_SCLK1 | out | D91 | AA3 | |||||

| GPIO5 | GPIO[5] | GPIO1 | D27 | F3 | dout2_p | dout2[0] | MPPC2 | in | D103 | AE3 | |||

| GPIO6 | GPIO[6] | D28 | F4 | dout2_n | dout2[1] | in | D102 | AF5 | |||||

| GPIO7 | GPIO[7] | D26 | F2 | dout_cmos2 | in | D101 | AD6 | ||||||

| GPIO8 | GPIO[8] | D29 | F5 | DAC_LDACn2 | out | D100 | AE6 | ||||||

| GPIO9 | GPIO[9] | D25 | G5 | DAC_PREn2 | out | D80 | V3 | ||||||

| GPIO10 | GPIO[10] | D30 | E1 | DAC_FS2 | out | D81 | V4 | ||||||

| GPIO11 | GPIO[11] | D24 | G4 | DAC_DIN2 | out | D82 | W1 | ||||||

| GPIO12 | GPIO[12] | D31 | E2 | DAC_SCLK2 | out | D83 | W3 | ||||||

| DAC_PREn0 | MPPC1_1 | out | D36 | D4 | dout3_p | dout3[0] | MPPC2 | in | D111 | AE1 | |||

| DAC_FS0 | out | D37 | C1 | dout3_n | dout3[1] | in | D110 | AE2 | |||||

| DAC_DIN0 | out | D38 | C2 | dout_cmos3 | in | D109 | AE5 | ||||||

| DAC_SCLK0 | out | D39 | C3 | DAC_LDACn3 | out | D108 | AF2 | ||||||

| DAC_PREn3 | out | D107 | AB7 | ||||||||||

| DAC_FS3 | out | D106 | AF3 | ||||||||||

| DAC_DIN3 | out | D105 | AF4 | ||||||||||

| DAC_SCLK3 | out | D104 | AD5 |

Firmware

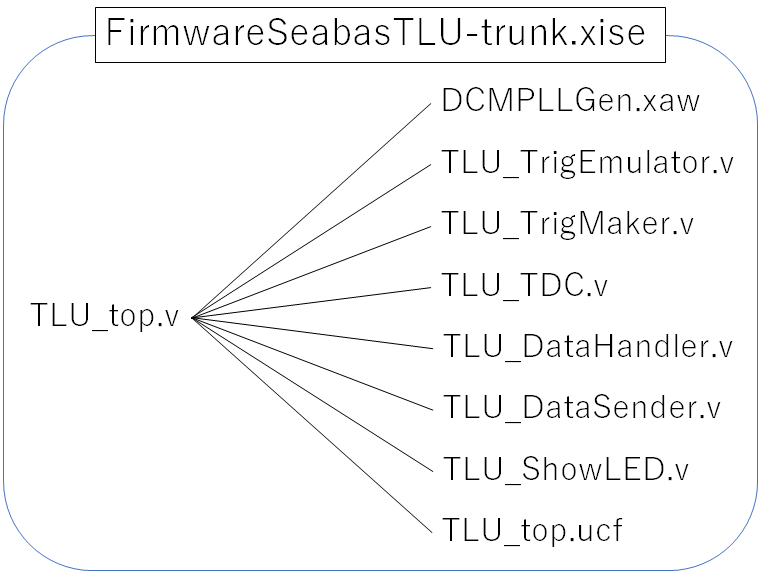

SeabasTLU-FNAL2/FirmwareSeabasTLU-trunk.xiseがSeabasTLUのprojectファイル ファイルに変更を加えた場合は上書き保存(ISEなら左上[Edit]下のフロッピーアイコンをクリック)する

コンパイルは、ViewがImplementationになっているのを確認してTLU_topを選択。Synthesize-XSTをダブルクリックまたは右クリックでRun(ReRun)をクリック

Synthesizeが終わったら、Implement Designをダブルクリックまたは右クリックでRun(ReRun)をクリック

終わったら、Generate Programming Fileをダブルクリックまたは右クリックでRun(ReRun)をクリック

ここまででerror

ファイルに変更を加えた場合は上書き保存(ISEなら左上[Edit]下のフロッピーアイコンをクリック)する

コンパイルは、ViewがImplementationになっているのを確認してTLU_topを選択。Synthesize-XSTをダブルクリックまたは右クリックでRun(ReRun)をクリック

Synthesizeが終わったら、Implement Designをダブルクリックまたは右クリックでRun(ReRun)をクリック

終わったら、Generate Programming Fileをダブルクリックまたは右クリックでRun(ReRun)をクリック

ここまででerror  が出なければコンパイルは成功しているので、Configure Target Device内のManage Configuration Project (iMPACT)をダブルクリックする

ISE iMPACT(別ウィンドウ)が立ち上がったらBoundary Scanをダブルクリックして、右側の範囲内で右クリック->Initialize Chainをクリック。そうするとSeabasに乗っているFPGAが認識される

TLUのプログラム焼くFPGAは右側なのでそちらを選択(緑色になってればOK)して、bitファイルを指定する(この後に別ウィンドウでDevice Programming Propertiesが出てきても特に関係ないのでOKを選択する)

Programをダブルクリック->Program Succeededが出れば完了!(PROMに書き込むかと聞かれたらNoを選択して下さい)

が出なければコンパイルは成功しているので、Configure Target Device内のManage Configuration Project (iMPACT)をダブルクリックする

ISE iMPACT(別ウィンドウ)が立ち上がったらBoundary Scanをダブルクリックして、右側の範囲内で右クリック->Initialize Chainをクリック。そうするとSeabasに乗っているFPGAが認識される

TLUのプログラム焼くFPGAは右側なのでそちらを選択(緑色になってればOK)して、bitファイルを指定する(この後に別ウィンドウでDevice Programming Propertiesが出てきても特に関係ないのでOKを選択する)

Programをダブルクリック->Program Succeededが出れば完了!(PROMに書き込むかと聞かれたらNoを選択して下さい)

DAC firmware

実装DAC-> TLV5630 --Comments

| I | Attachment | History | Action | Size | Date | Who | Comment |

|---|---|---|---|---|---|---|---|

| |

110520seabas2a.pdf | r1 | manage | 454.4 K | 2018-01-31 - 06:14 | AtlasjSilicon | |

| |

DSC_0001.jpg | r1 | manage | 1276.9 K | 2018-01-31 - 12:45 | AtlasjSilicon | |

| |

DSC_0003.jpg | r1 | manage | 999.0 K | 2018-01-31 - 12:45 | AtlasjSilicon | |

| |

ISE_error.png | r1 | manage | 0.5 K | 2018-02-03 - 08:23 | AtlasjSilicon | |

| |

ISE_ok.png | r1 | manage | 0.6 K | 2018-02-03 - 08:23 | AtlasjSilicon | |

| |

ISE_warning.png | r1 | manage | 0.5 K | 2018-02-03 - 08:23 | AtlasjSilicon | |

| |

SeabasTLU.png | r1 | manage | 33.9 K | 2018-02-03 - 08:23 | AtlasjSilicon | |

| |

tlv5630.pdf | r1 | manage | 1155.8 K | 2018-01-31 - 06:14 | AtlasjSilicon |

Topic revision: r9 - 2018-02-05 - AtlasjSilicon

Ideas, requests, problems regarding TWiki? Send feedback