Difference: TLUfirmware (22 vs. 23)

Revision 232018-03-02 - AtlasjSilicon

TLUfirmwareTLUadapter boardTLUadapter board ver.B-> 表、-> 裏 adapter boardのNIMinは50 ohm terminationが必要となるので、 別途実装する 設計ミスでSEABASのJ1とJ3どちらか片方にしか接続できない問題(新しいものでは解決済み) Kyocera connector側:NIMinが回路図と反対側に繋がっていた->不幸なことに一部がADCと繋がっている(FPGAと繋がっていない)J3 connector側であり、SEABAS上での接続先がそのADCにあてがわれていた Integration testではJ3に接続するつもりだったconnectorをSEABAS側J2に接続する(J1は未接続、JTAGが干渉してadapter boardはSEABASにしっかりとは刺さっていない) SEABASのFPGAではLVDS信号は扱えない(ucfファイルで指定しようとすると怒られる)のでB'版ではLVDS->CMOSのICを実装する 波形が出ない場合はPIN assignが間違っていないか確認する ->基本的にucfファイルを編集する。どのPINが何に使われているかを一覧で見たい場合はPlanAheadを起動すると分かりやすい https://docs.google.com/spreadsheets/d/12SCUal2avY3kW65fRVte5TG3hSL1h8-VrYYAfBwH4Lk/edit?usp=sharing

| ||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

| Changed: | ||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

| < < | 本番用 | |||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

| > > | 本番用(3/1更新) | |||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

| ||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

| Changed: | ||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

| < < |

| |||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

| > > |

| |||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

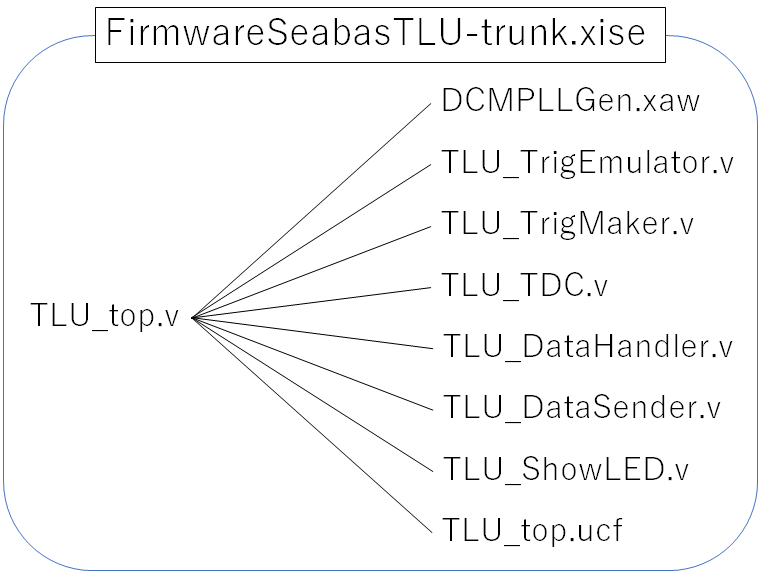

FirmwareSeabasTLU-FNAL2/FirmwareSeabasTLU-trunk.xiseがSeabasTLUのprojectファイル ファイルに変更を加えた場合は上書き保存(ISEなら左上[Edit]下のフロッピーアイコンをクリック)する

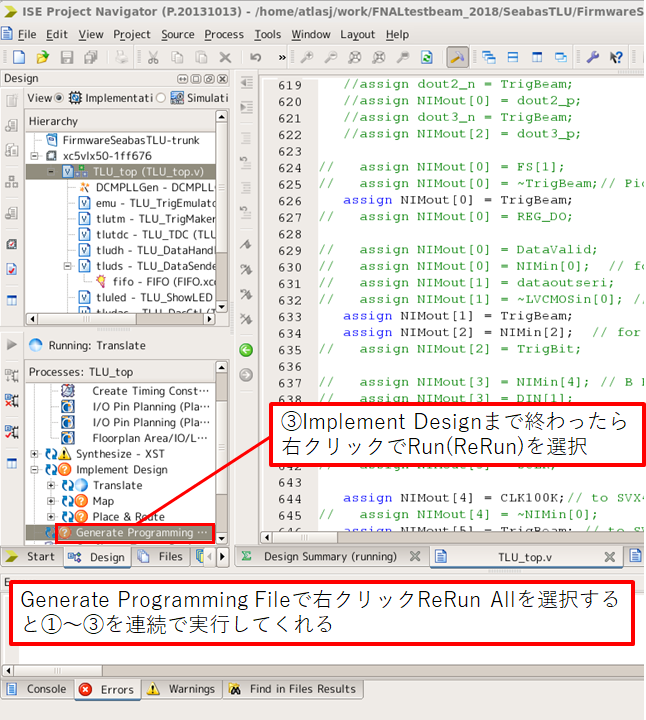

コンパイルは、ViewがImplementationになっているのを確認してTLU_topを選択。

ファイルに変更を加えた場合は上書き保存(ISEなら左上[Edit]下のフロッピーアイコンをクリック)する

コンパイルは、ViewがImplementationになっているのを確認してTLU_topを選択。

<--/twistyPlugin twikiMakeVisibleInline-->

############コンパイルの仕方############

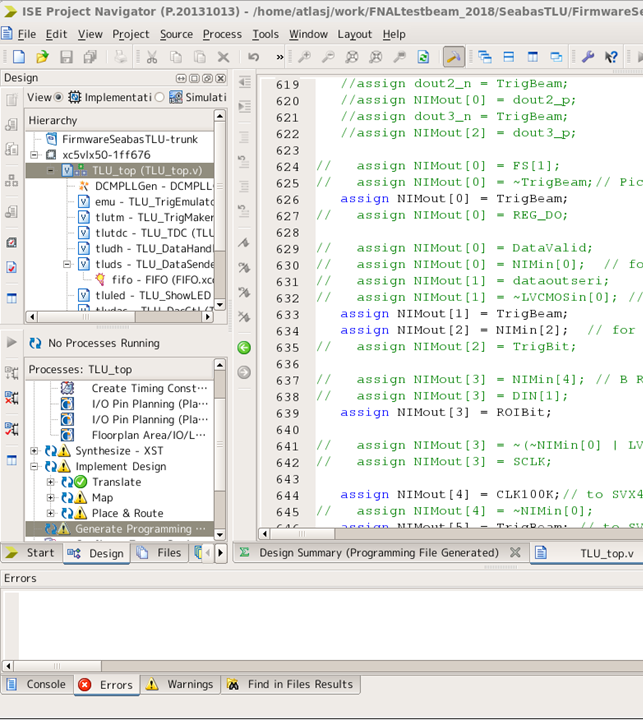

↑のようになっていればコンパイルは成功している

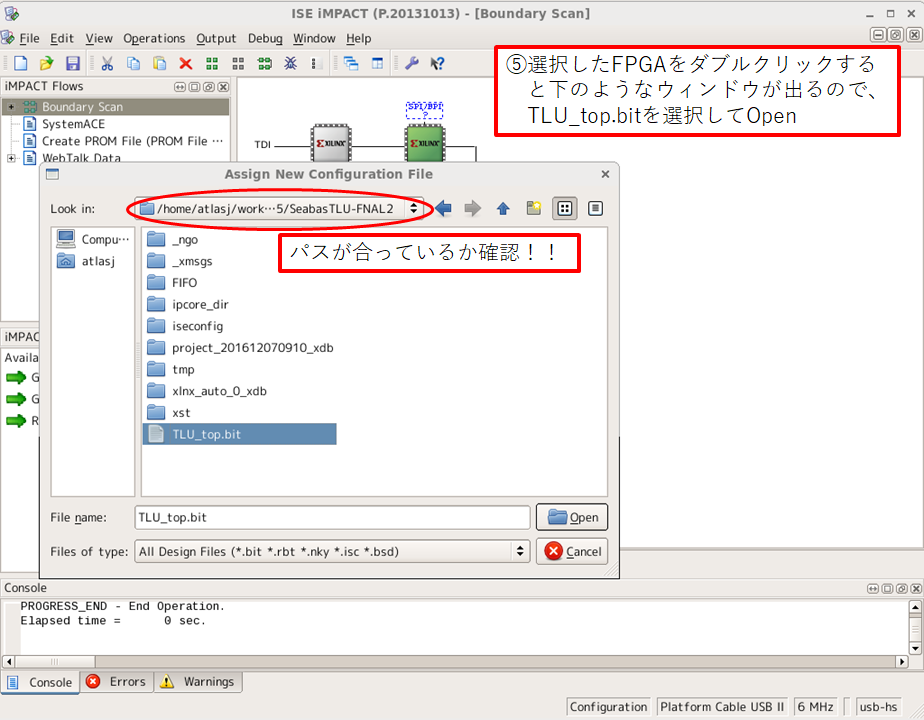

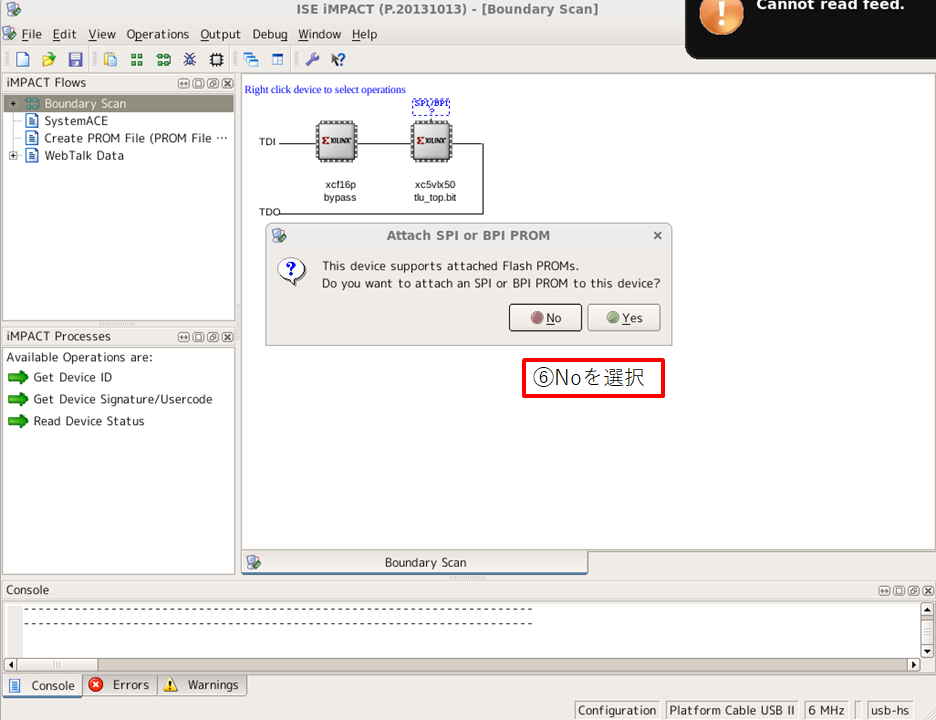

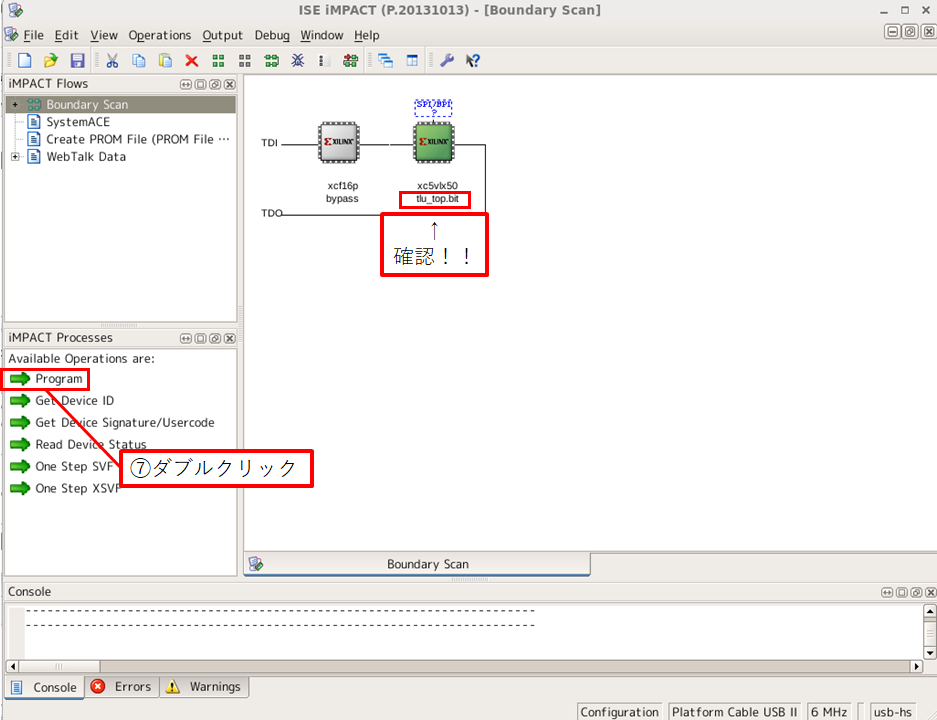

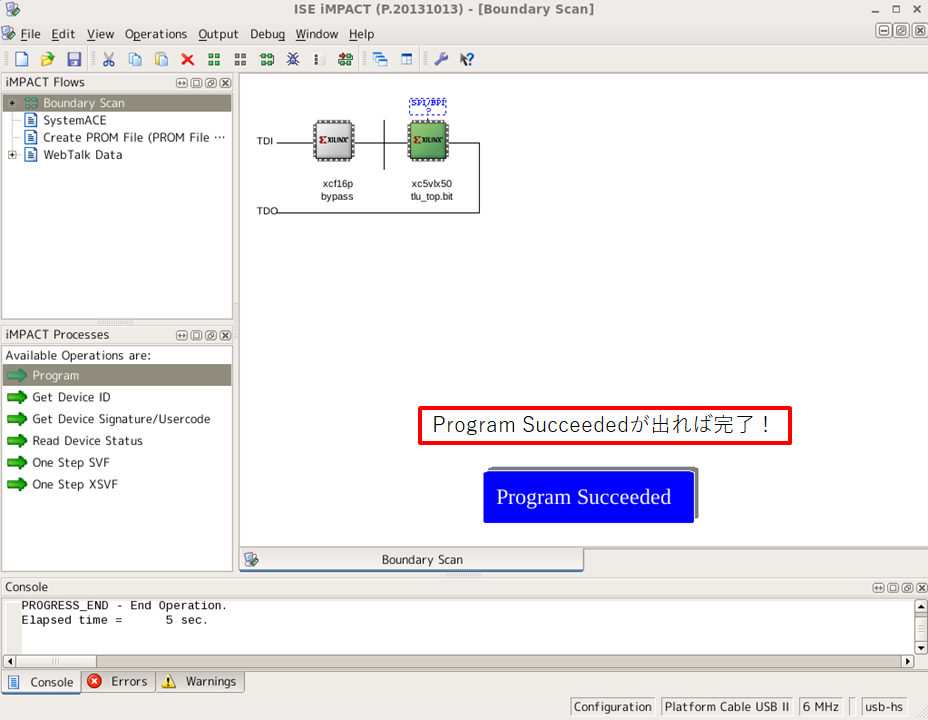

############FPGAへの焼き方############

↑のようになっていればコンパイルは成功している

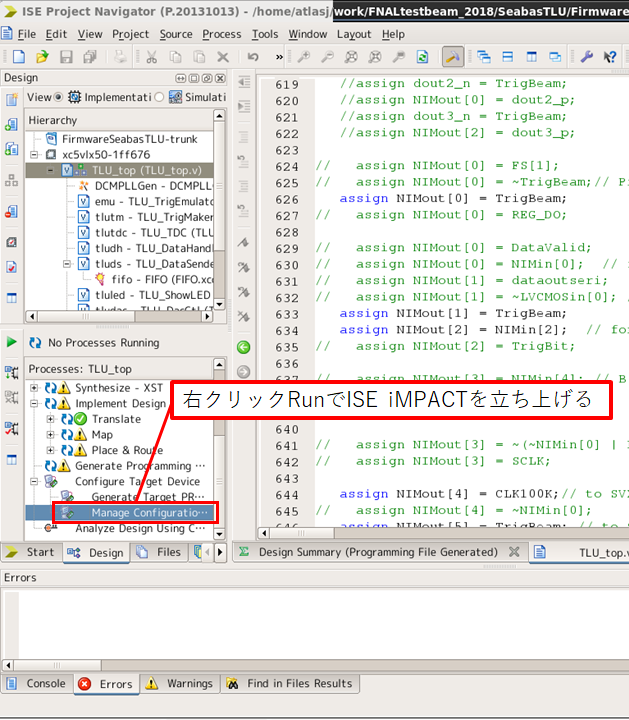

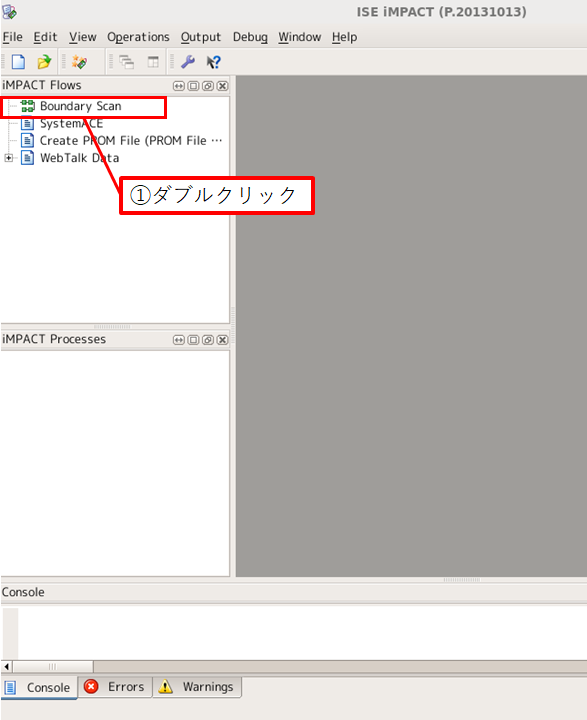

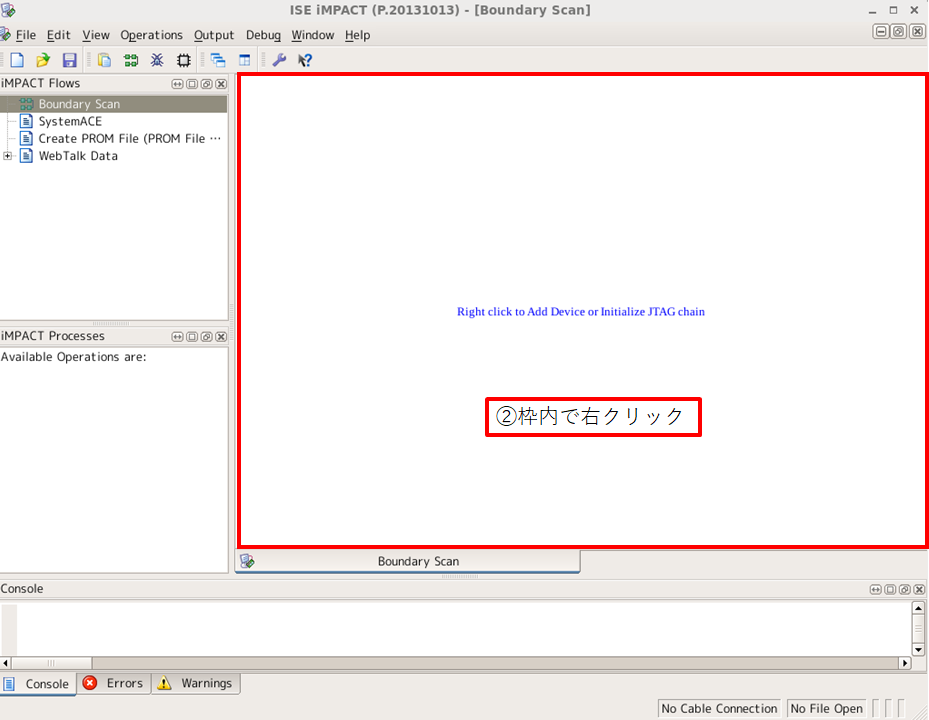

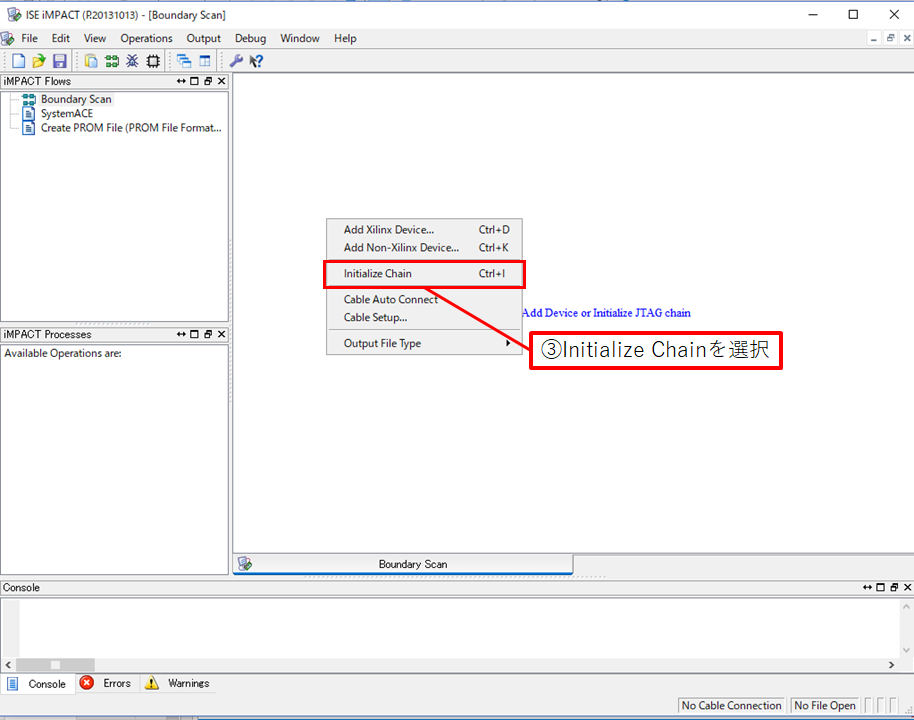

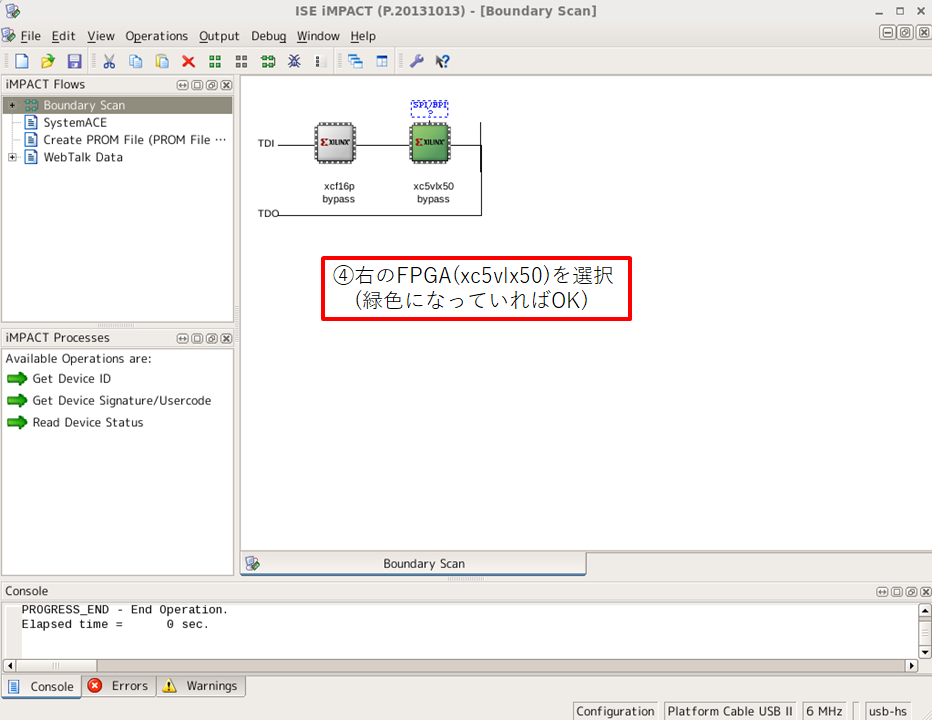

############FPGAへの焼き方############

そうすると別ウィンドウでISE iMPACTが立ち上がる

以降はSEABASがJtagで接続されていることを前提としている

そうすると別ウィンドウでISE iMPACTが立ち上がる

以降はSEABASがJtagで接続されていることを前提としている

<--/twistyPlugin--> DAC firmware実装DAC-> TLV5630 --Comments

| ||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

View topic | History: r23 < r22 < r21 < r20 | More topic actions...

Ideas, requests, problems regarding TWiki? Send feedback