| |

| META TOPICPARENT |

name="WebHome" |

RD53A DAQ Development

Introduction |

| | --  Ryo Nagai - 2016-10-17 Ryo Nagai - 2016-10-17

FE-I4 Readout Test |

|

<

< |

- FPGA Hardware and Additional apparatuses

|

>

> |

- FPGA Hardware and Additional apparatuses

|

| |

-

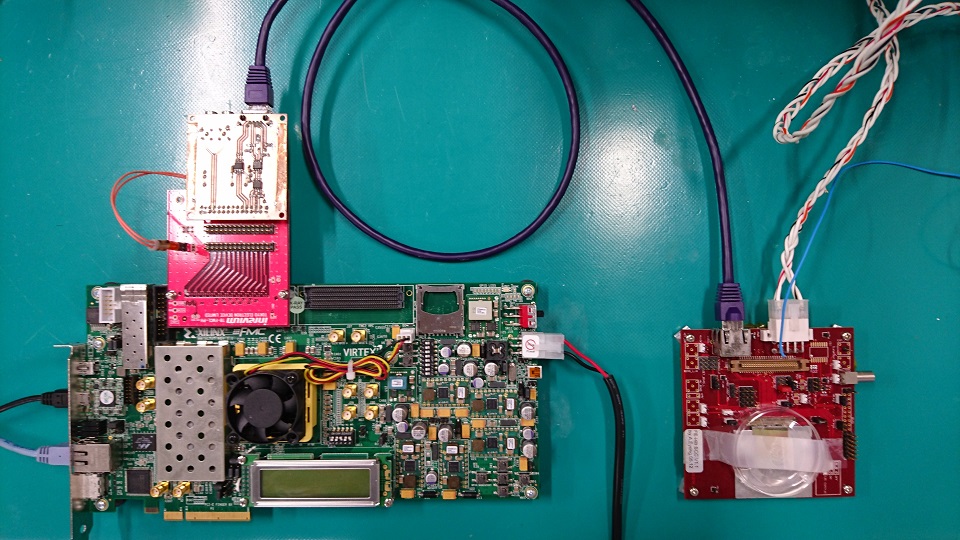

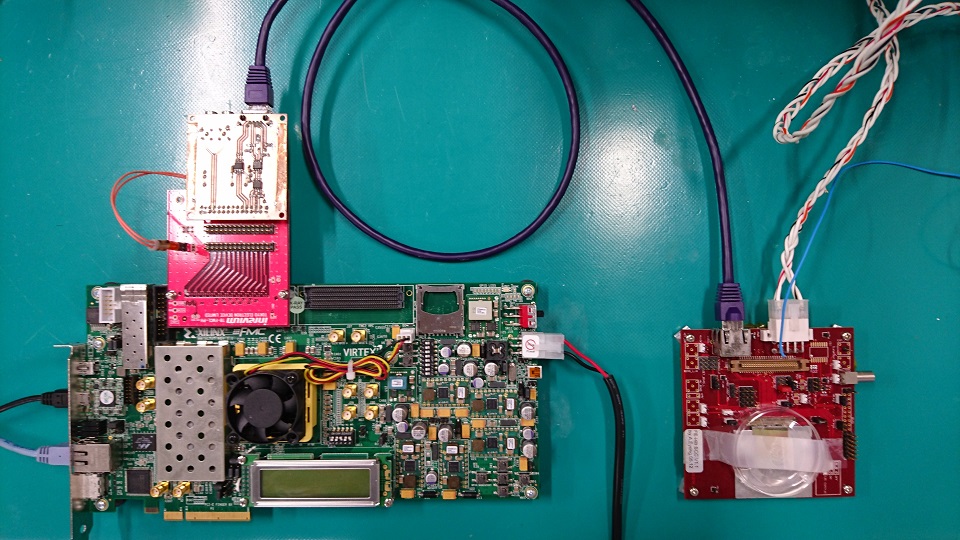

- FPGA Hardware

- Prerequisites

Target devices : Virtex-7 VC707 Evaluation Platform (xc7vx485tffg1761-2)

Tool Version : Xilinx Vivado 2015.4 or later tools

If you are using Kintex-7 KC705 Evaluation Platform, you need to change the SiTCP module in the firmware to XC7KSiTCPlib32k.

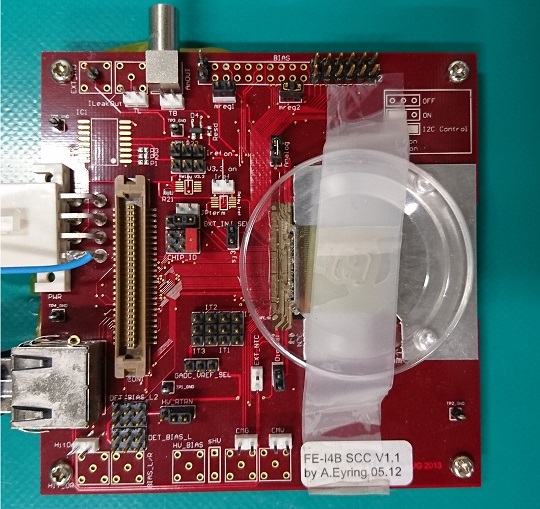

- FEI4B Single Chip Card

|

|

<

< |

-

-

- RJ45/FMC - SLVS/LVDS Conversion Board

|

>

> |

-

-

- RJ45/FMC - SLVS/LVDS Conversion Board

- TB-FMCL-PH board (inrevium TOKYO ELECTRON DEVICE)

- used for conversion between Samtec FMC connector (Low-Pin Count) and 2.54mm pitch pin header.

- SLVS <-> LVDS level shiter designed by Ryo Nagai: LVDS2SLVS_Pins.zip

- Hardware setup

- Example

|

| |

- DAQ Software

|

|

>

> |

-

- How to config FEI4

- For example, execute on your terminal run 1 0111 which is a command to do "Digital Injection and mask chip_1 to chip3."

Please refer to SEABAS2 DAQ Usages.

|

| |

- Release

|

|

<

< |

- Notes (日本語暫定簡易版)

- FMC LPCのピン配置は阪大で使用しているテスト用変換基板のピン配置に準拠しています。それ以外の変換基板を利用の際は制約ファイルを編集してピン配置を変更する必要があります。

- 現在、論理合成時のエラーは既知のものです。無視して構いません。どうしても気になる方は修正をお願いします。

- インプリメンテーション時にタイミング違反の警告メッセージが出ますが無視してください。重要でない場所です。

- FEI4B SCCにConfigが通ることまで確認しています。こちらの動作の都合で、FEI4からの受信データをPCへTCPで転送できているかどうかは6/25時点でまだ未確認です(澤田)。

|

>

> |

- Notes

- When you use the original conversion board, you need to change the pin assignment to comply with your board.

(Default firmware is build for a setup of Osaka Univ.)

- Already-known warnings

- Redundant IBUF can be ignored.

- Status report

- (6/26) Succeeded in configuring FE-I4B and confirmed the response of the data signal. Problems remain in iserdes, 8b10b decoder part. by Sawada

|

| | Tips |

| |

| META FILEATTACHMENT |

attachment="OFTC_ref_note.pdf" attr="" comment="" date="1495691192" name="OFTC_ref_note.pdf" path="OFTC_ref_note.pdf" size="48837" user="AtlasjSilicon" version="1" |

| META FILEATTACHMENT |

attachment="references.pdf" attr="" comment="" date="1495693148" name="references.pdf" path="references.pdf" size="892748" user="AtlasjSilicon" version="1" |

| META FILEATTACHMENT |

attachment="LVDS2SLVS_Pins.zip" attr="" comment="" date="1495793797" name="LVDS2SLVS_Pins.zip" path="LVDS2SLVS_Pins.zip" size="217304" user="AtlasjSilicon" version="1" |

|

|

>

> |

| META FILEATTACHMENT |

attachment="FEI4BSCC.jpg" attr="h" comment="" date="1498471156" name="FEI4BSCC.jpg" path="FEI4BSCC.jpg" size="136127" user="AtlasjSilicon" version="1" |

| META FILEATTACHMENT |

attachment="VC707_setup.jpg" attr="h" comment="" date="1498471264" name="VC707_setup.jpg" path="VC707_setup.jpg" size="225804" user="AtlasjSilicon" version="1" |

|