RD53A measurement Log

- RD53A measurement Log

- そもそもconfigが通らない問題

- LDO modeでconfigが通らない問題

- threshold scan問題

- digital scan問題

- CardGND"> Single Chip CardのGND問題

- RD53A module Assembly

- Module Testing

- KEK53-3

- KEK53-4(STD)

- KEK53-5(STD, irrad)

- KEK53-6(Small Al)

- KEK53-7(25x100um)

- KEK53-8(25x100um, irrad)

- KEK53-9(thick SiO2 between Poly-Si & Al)

- KEK53-10(thick SiO2 under BR, irrad)

- KEK53-11(thick SiO2 under BR)

- KEK53-12(Poly-Si : 0.67MΩ/pixel)

- KEK53-13(Poly-Si : 6MΩ/pixel, irrad)

- KEK53-14(Small Al, thick SiO2 btw PolySi-Al, Poly-Si : 6MΩ/pixel)

- KEK53-15(Small Al, thick SiO2 btw PolySi-Al, Poly-Si : 6MΩ/pixel, irrad)

- KEK53-16(Small Al, Poly-Si : 6MΩ/pixel)

- KEK53-17(Small Al, Poly-Si : 6MΩ/pixel, irrad)

- Sync & Lin FEs disable

- bias railをGNDに落とす

- Comments

>>>>>

July CERN TB log<<<<<

########################################################################################################

抱えている問題点

-

configが通らない : チップにdirect modeの動作電圧(VDDD=1.3V , VDDA=1.3V)がかかるようにLVを調整すると通るようになった

-

direct modeにおいてTEXIOで両方1.3Vかけてもチップに正常な電圧が流れない(だいぶ低くなる) : 4pin connectorの接触抵抗?→connectorをKEKで使っているものに付け替え→改善

-

LDO modeでconfigが通らない(KEK53-3) : 電源の立ち上がり?、電圧不足?、LDOが壊れてる?→LDOでは動きそうにないので以降はdirectで動かす

-

digital scan問題 : 数時間放置→元に戻った→おそらくdigital current問題

-

SCC のGND問題 : pico太郎プローバーでPORのGNDを挟む(PC=Xpressk7とSCCのGNDを共通にする)→USBpixを電源として使う→micro USB to 4pin基板でTEXIOとPCのGNDを共通にする

-

std threshold scanが途中で落ちる : メモリーリーク?→software updateで対処

-

tune thresholdのあとにthreshold scanを行うと落ちる : メモリーリーク?→同上

-

scan中またはscan後にdigital currentが上がる問題→現状この症状は確認されない

########################################################################################################

そもそもconfigが通らない問題

- source /opt/Xilinx/Vivado/2016.4/settings64.shをして、vivadoでVivadoを起動

- Open Hardware Manegerに入り、Open targetのAuto connectをクリック

- xcf7k325t_1を右クリックし、Program Deviceをする

- ~/work/FNALTestbeam2018/XpressK7_RD53A/YARR-FW/syn/xpressk7/bram_rd53a_quad_lbnl-325内のrd53a_quad_lbnl_passive_325_160Mbps_pixregro.bitを焼いてPCをreboot

- src内で"./bin/test"を実行して正常に動くかを確認

vivado をsource した後にpython flash.py をするとbitファイルのリストが表示されるので、ここでファイルを指定しても焼くことができる。この場合はメモリにも書かれるので少し時間がかかる。焼いた後は同じくreboot必須。

./bin/test が問題なく動いたらRD53Aと接続、電源を投入して ./bin/rd53a_test を実行し、

[Data] : COL(12) ROW(1) PAR(1) TOT(15,11,15,15)

のような結果が得られれば、config が通っている。

※YARRのversionでinjectionしているpixelが変わっていることがあるのでversion up等された場合は必ずrd53a_testの中身を確認すること!

現状PC10だとPCIeでXpressk7が認識されていないっぽいのでPC9でテスト中

LVはTEXIOから供給すると立ち上がりが遅いため(?)に動かない確率が高い。代用としてUSBpixのregulatorを用いると応答の確率が高い?

→テスターで測定しながらVDDD、VDDAが1.3Vとなるように調節してTEXIOから電圧をかけるとconfigが通った(安定している)

scanの途中にconfigが崩れることが割とある

LDO modeでconfigが通らない問題

Vin:1.8Vをかけてもconfigが通らない、そもそも何も返ってこない

SCCの表面実装をrecommendationに対応させた→

Single Chip Card への変更点→それでもconfig通らず

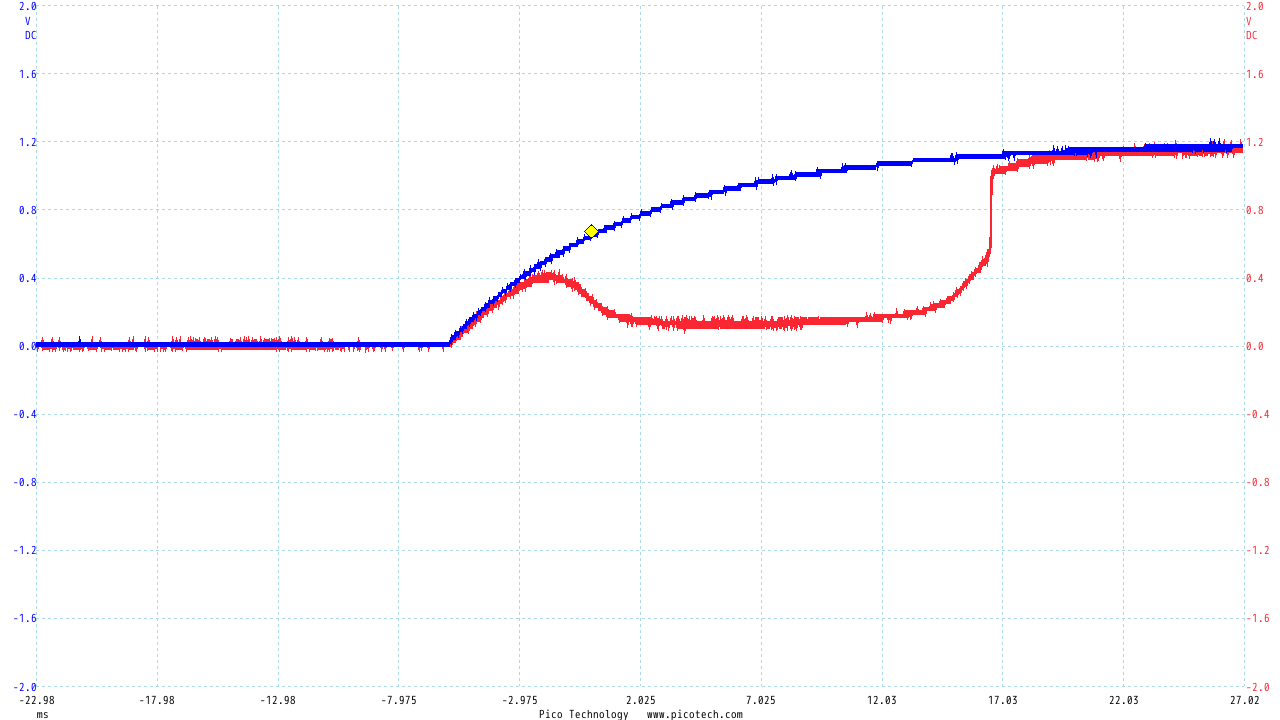

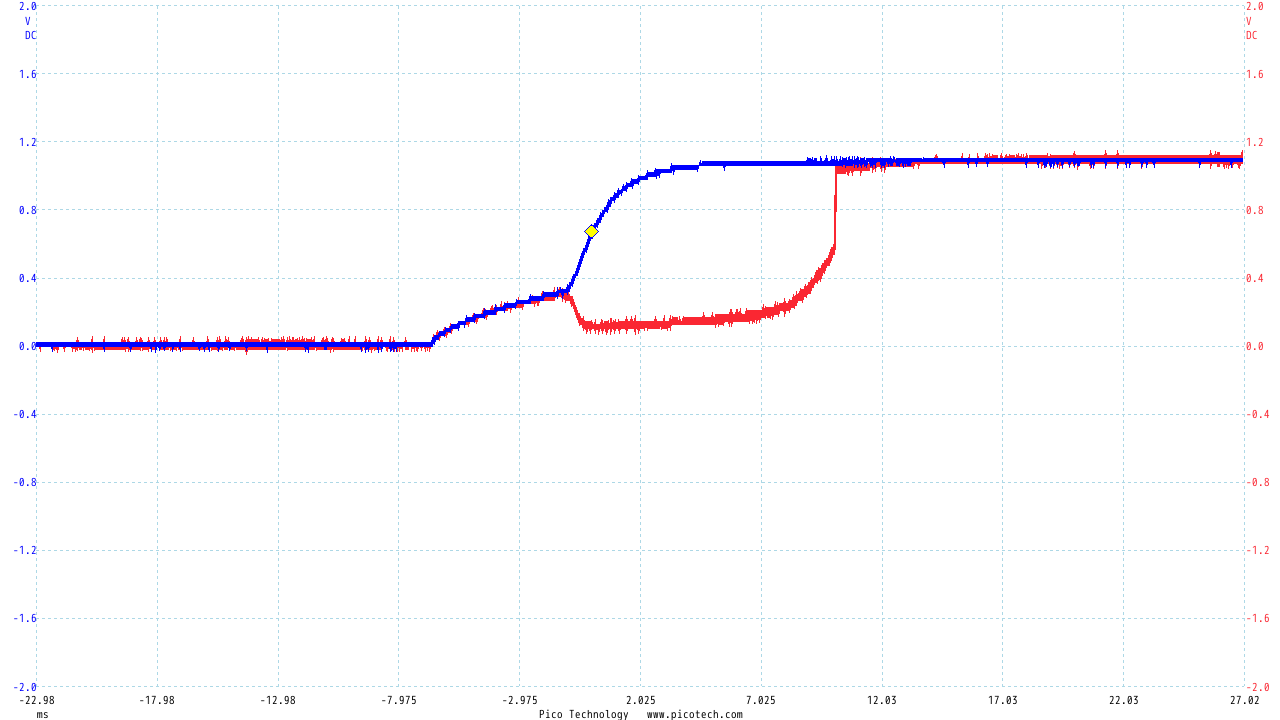

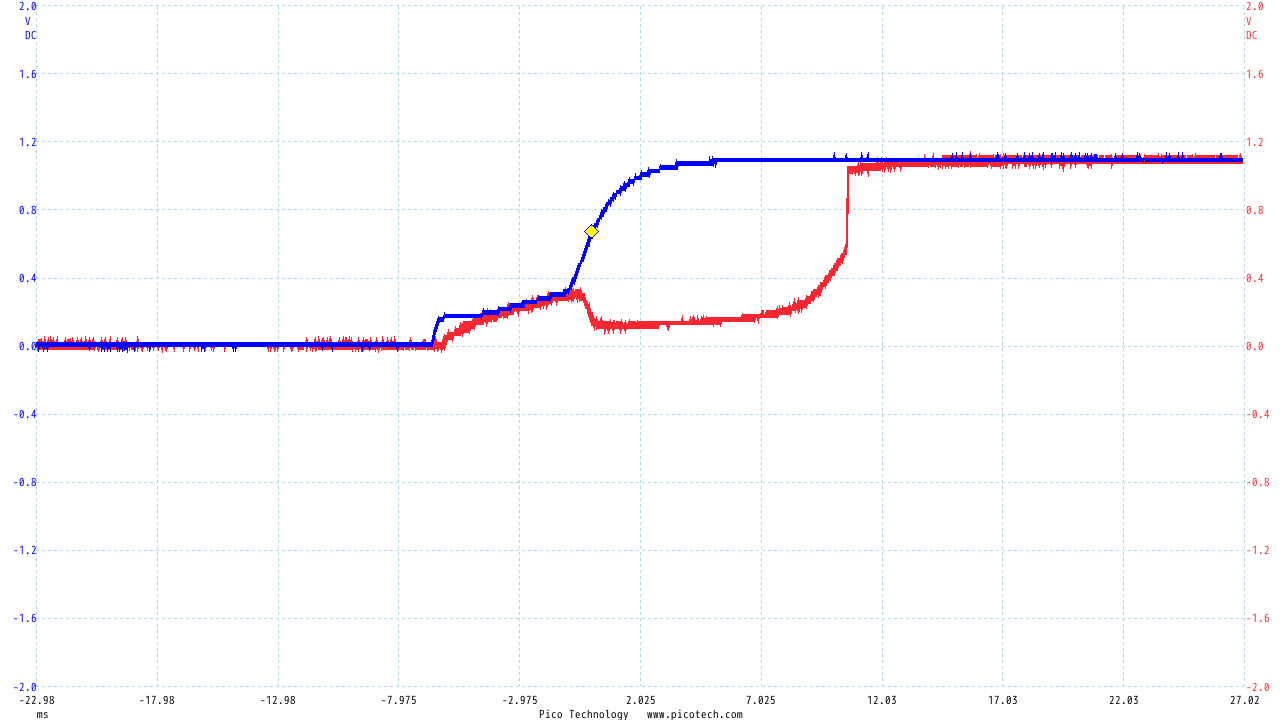

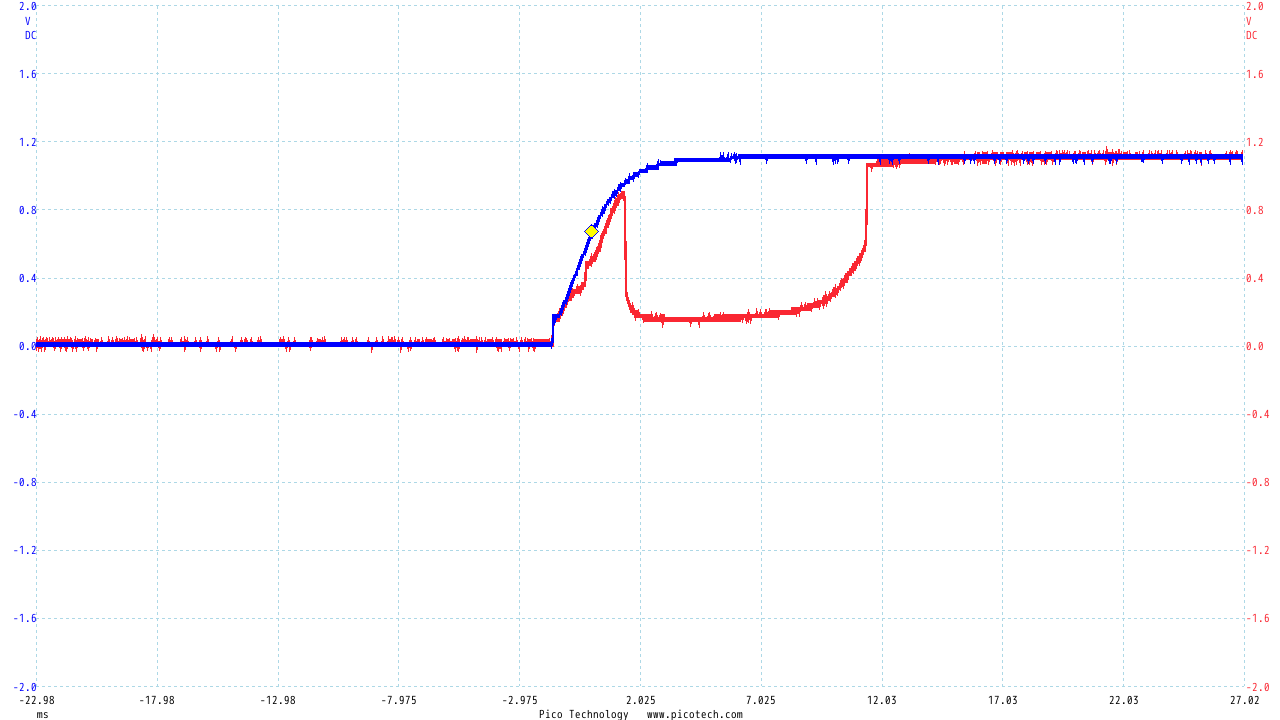

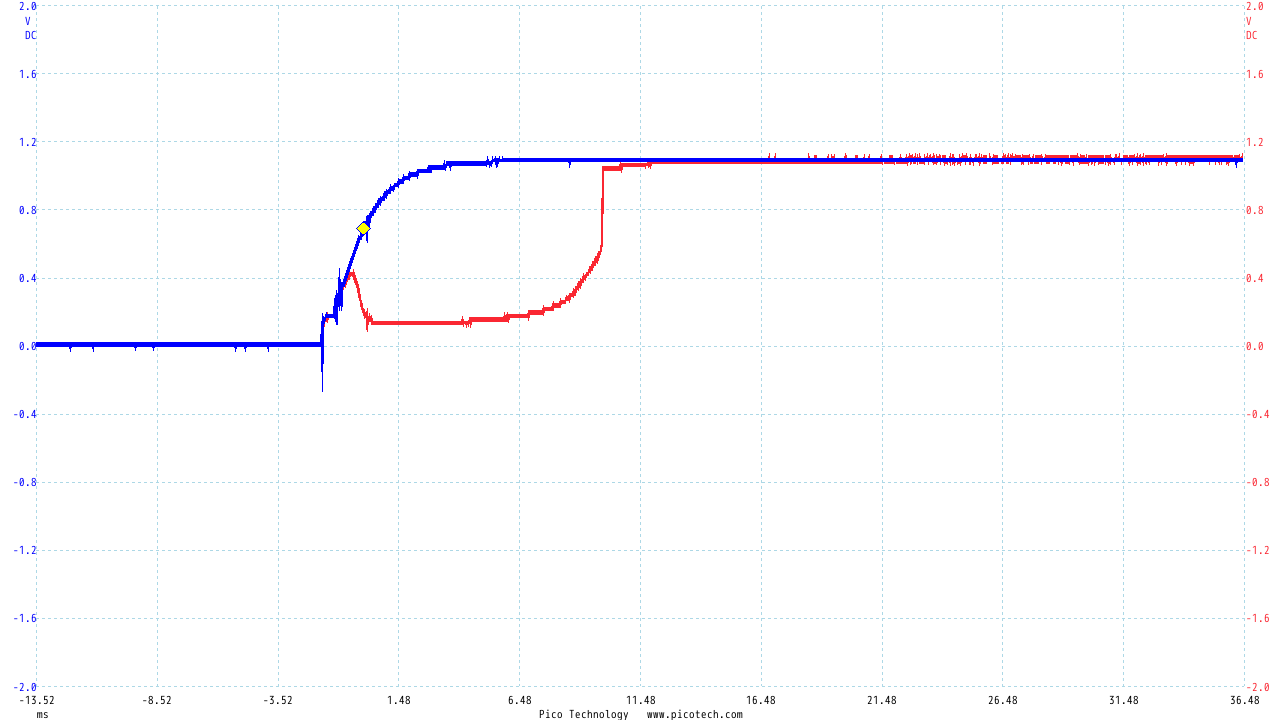

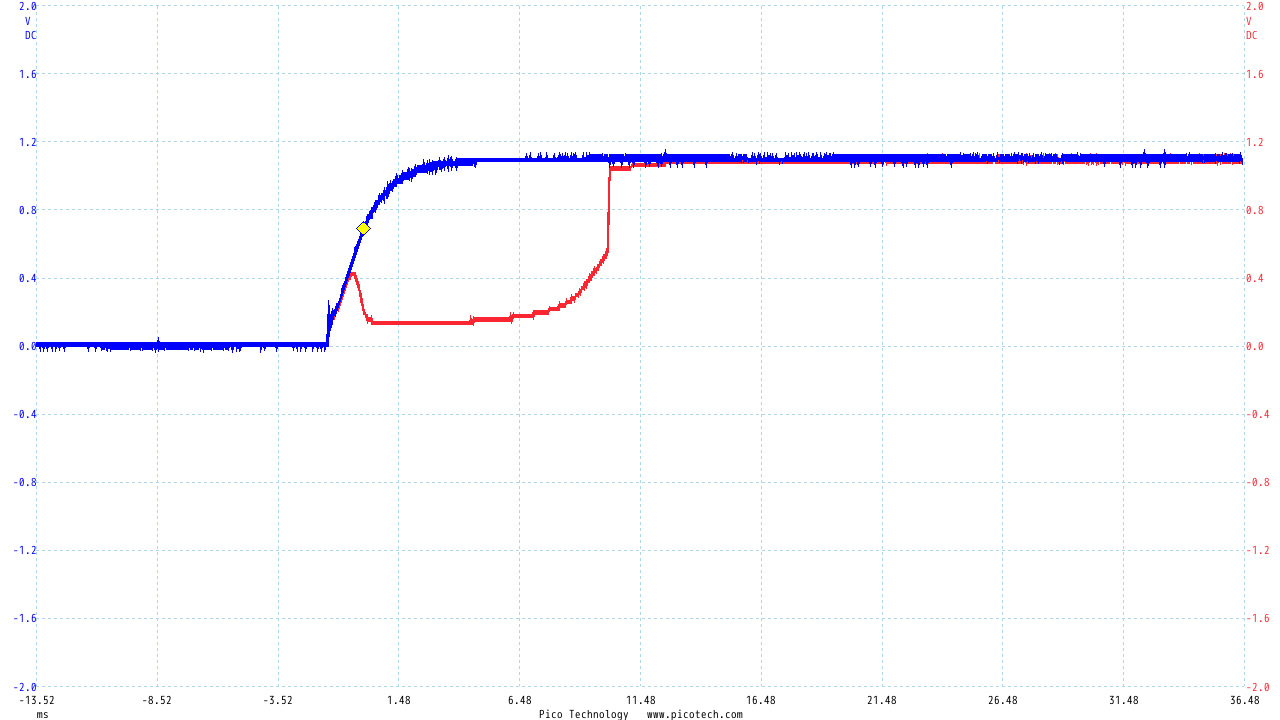

電源の立ち上がりが安定する前にPORが立ち上がるとconfigが通らないため、PORが働くまでのdelayをpico太郎で見てみる

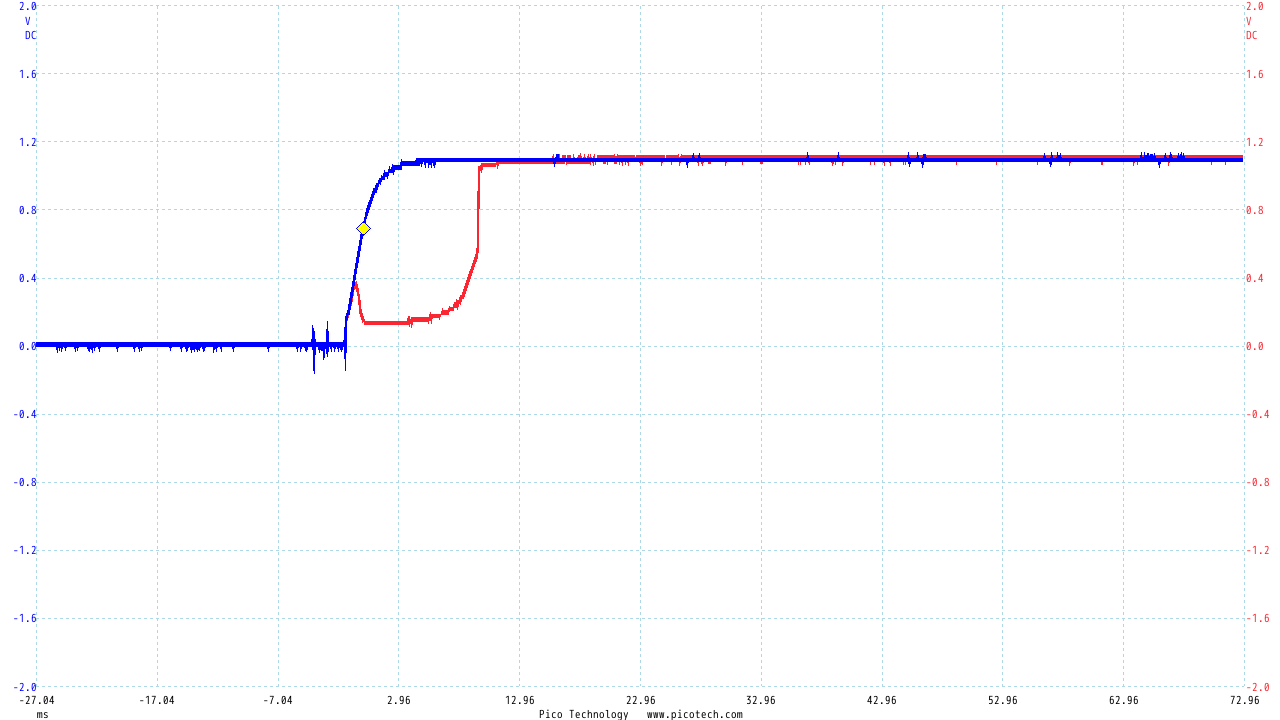

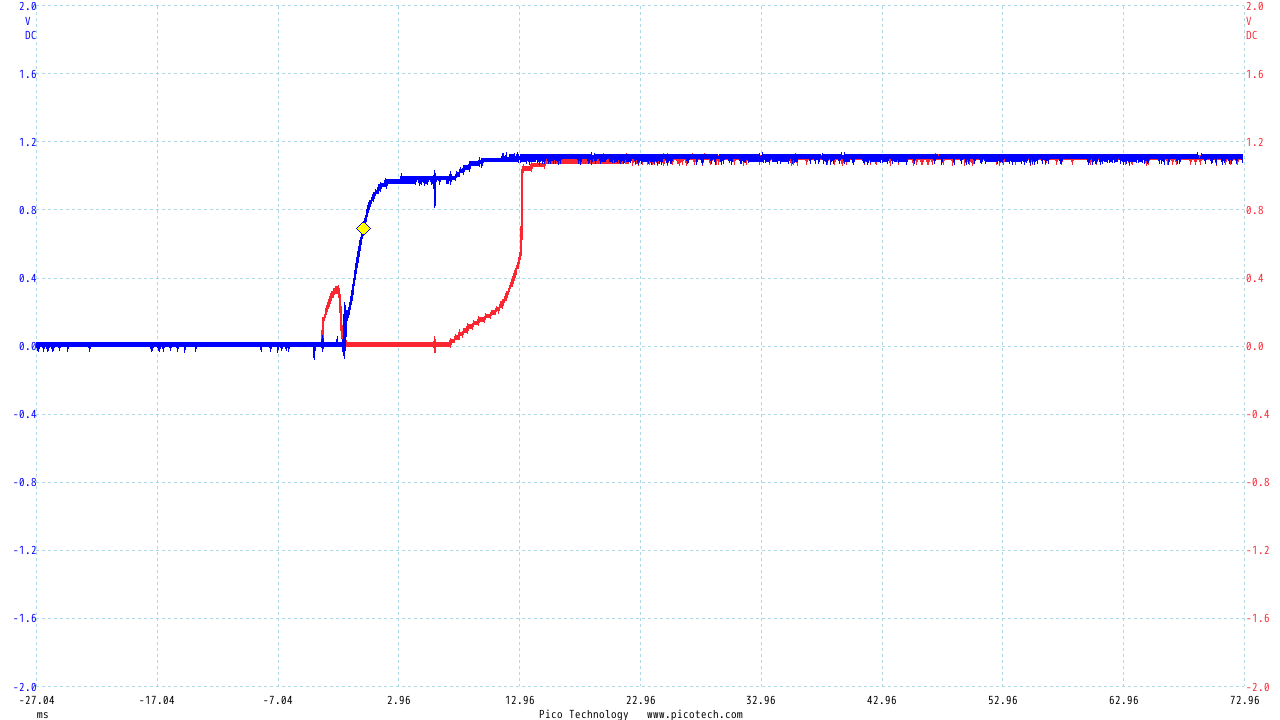

TEXIOだとやはり電源の立ち上がりが遅い?(ただ立ち上がりの遅いdirect modeだとconfigが通る)→立ち上がりの早いUSBpixのregulatorを使ってみる

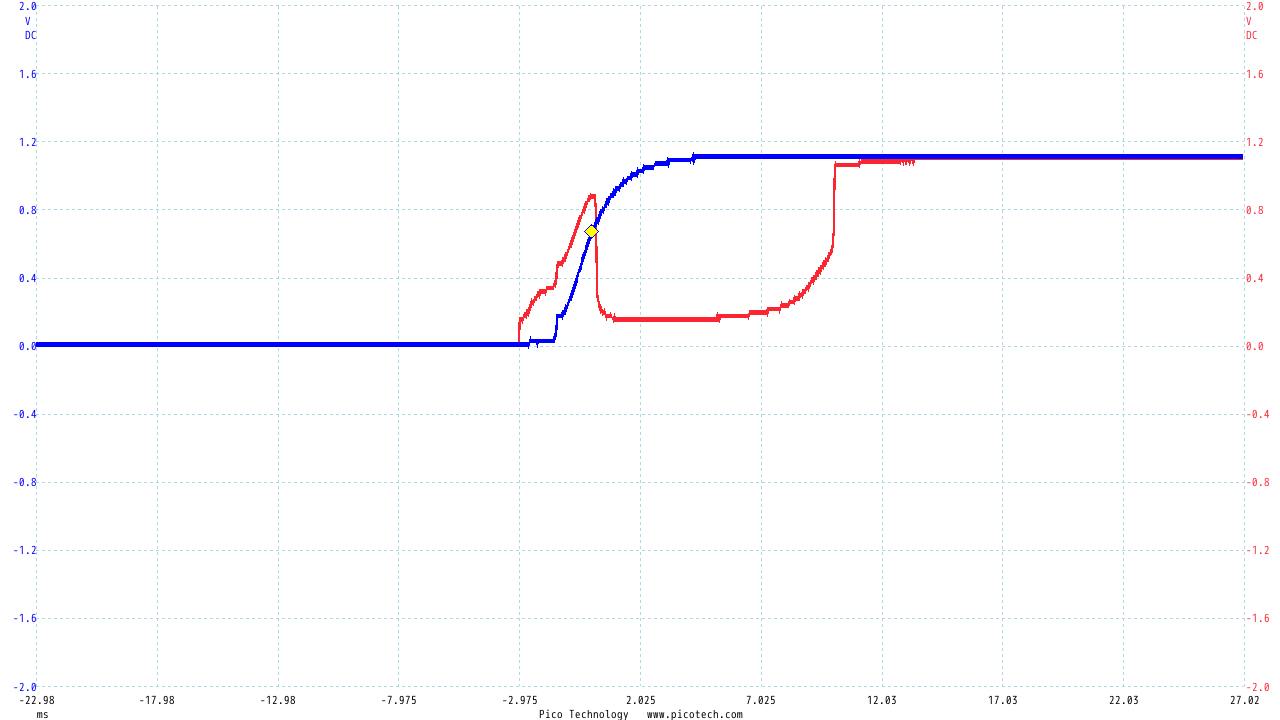

USBpixだとVDDDの立ち上がりがVDDAと比べて遅くなってしまっている(現状原因不明)

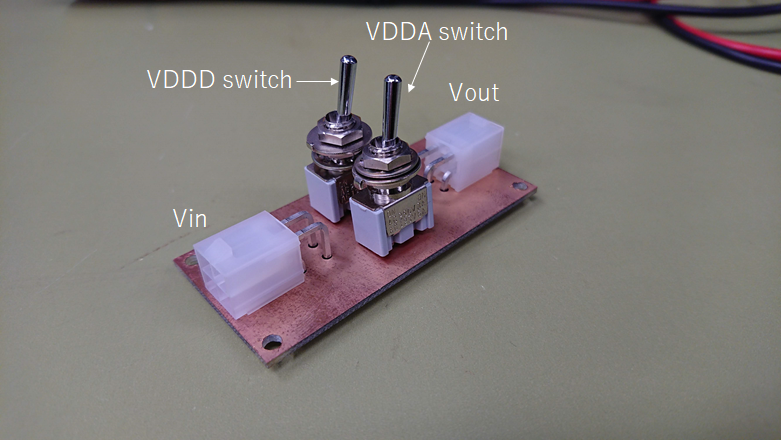

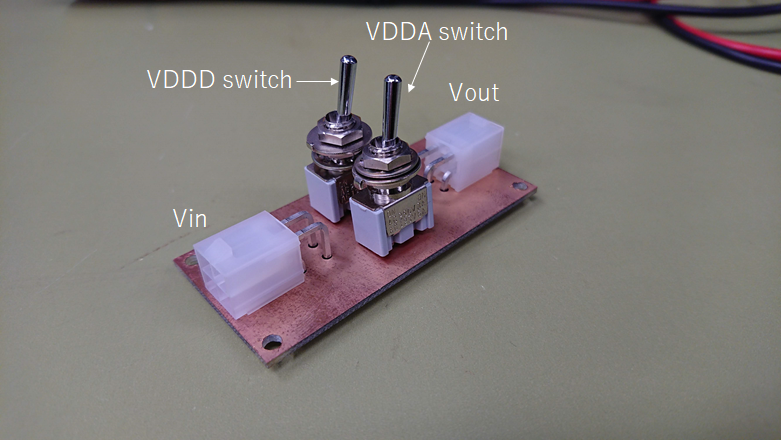

メカニカルスイッチを使うと立ち上がりが早くなる?→バウンドが懸念?

VDDD,VDDA用にスイッチが2つ付いているが、手でonするため同時性が保証されない

それぞれをonする相対時間が長いとPORが立ち上がるタイミングが冗長となる(?)

メカニカルスイッチのVout側をショートさせて1つのスイッチでVDDD/VDDAがかかるように改造

同時にonできるので、冗長性が消えたが、VDDAの立ち上がり始めに少しステップが見られる

立ち上がり問題とは別に、regulatorで作ったVDDD/VDDAが低い問題もある

register書き換えでregulatorのVoutは変えられる→そもそもconfigが通らないと反映されない

外部からの電圧(Vin)を高くしていくと、Voutも高くなっていく(?)→1.8Vから2.0Vまで上げてみたが6mV程度しか上がらなかった

threshold scan問題

std threshold scanがtune前後関係なく落ちる

lin/diff threshold scanに関してはtune後(tuneはlin/diff問わず)に落ちるようになる

topを見ながら走らせるとメモリーを使い果たしたことでjob自体がkillされている→メモリーリークか

src/libRd53a/Rd53aDataProcessor.cpp内の m_outMap->at(activeChannels[i]).pushData(curOut[activeChannels[i]]);を if(events[activeChannels[i]] > 0)の中に入れてコンパイルし実行

→メモリーリーク直らず

digital scan問題

direct mode、それぞれVDDD=1.23V,VDDA=1.20Vをかけた状態でdigital scanを行ってもうまく返ってこない

dig/anaの電流値を見る限りconfigが通っていそう

rd53a_testを走らせると、最初良さそうな結果が返ってくるが、ノイズが以前よりも大分多くなってしまっている

数時間放置したら正常な動作に戻った、なぜ急に調子が悪くなったのかは不明

CardGND"> Single Chip CardのGND問題

direct mode,LDO modeに関わらず、TEXIO power supplyだとPORピンのGNDをpicoscopeのプローバーGNDで挟まなければdigital scanが返ってこない→SCCのGNDが浮いているため?

picoscopeはUSBでDAQ PCと接続されており、PCIe(Xpressk7)とGNDが共通→Xpressk7とSCCのGNDを共通にするとdigital scanが返ってくる

USBpix power supplyだとプローバーGNDで挟まなくてもdigital scanが返ってくる←USBpixのGNDがPCと共通=電源のGNDがPCと共通

TEXIO power supplyでもGNDを挟まずにscanが出来るように中村さんがmicro USB to 4pin基盤を試作 USB cableでPCに繋ぎ、4pinでGNDだけTEXIOに繋ぐ(設計上5V電源としても使えるようになっているが今は使用しない)

TEXIO power supplyでGND共通にしなくてもdigital scanが返ってくるようになった?

RD53A module Assembly

6/14にHPKからBBされたRD53A moduleが届いたのでSCCにアセンブリ

本日のモジュール。

アルミはアラルダイトを用いてSCCに接着。→

Fig

今回ネジ穴がカバーとアルミ同じ。

アルミとmodule(ASIC+sensor)は熱伝導接着剤(

J-Themo03M)で接着→

Fig

照射するために熱の伝わりやすいの接着剤を使用。

室温だと固まるのに二日かかるため、70°で二時間温めた。

インジウムバンプは85°までしか耐性がないため注意すること。

ワイヤーボンディング→以前に試し打ちをしたもののせいか、一部うまくいかないことあり。(58ぇ・・・)

センサー名(仮)4-5→

KEK53-4

センサー名(仮)4-6→ KEK53-5

6/27に新しく8枚届いた

2-3(条件7,single1,

Red chip)→KEK53-13

2-5(条件5,single1,

Yellow chip)→KEK53-12

4-3(条件1,single3 ①)→KEK53-7

5-4(条件1,single3 ②)→KEK53-8

4-4(条件1,single2)→KEK53-6

5-5(条件2,single2)→KEK53-9

5-9(条件3,single1 ①)→KEK53-10

5-10(条件3,single1 ②)→KEK53-11

9/6に新しくmodule(恐らくノイズが一番小さいもの)が届いたのでAssembly

6-10(条件8,①)→KEK53-?

6-11(条件8,②)→KEK53-?

Module Testing

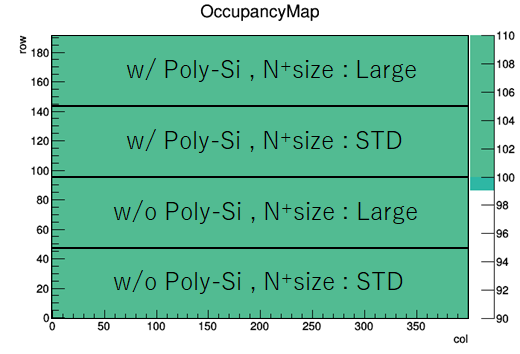

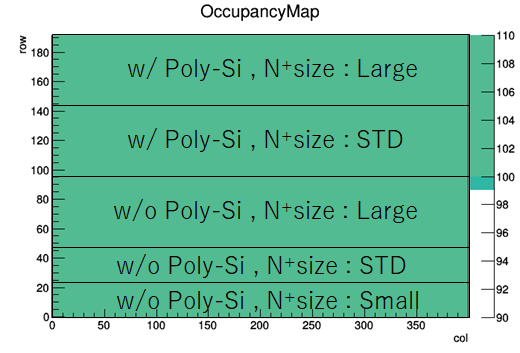

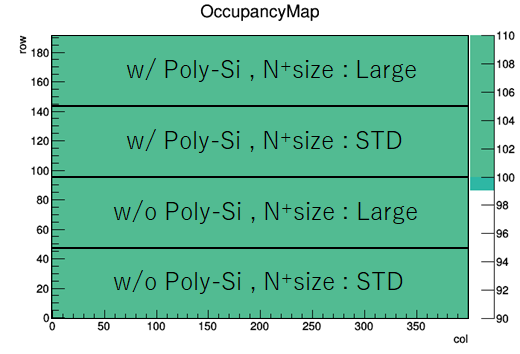

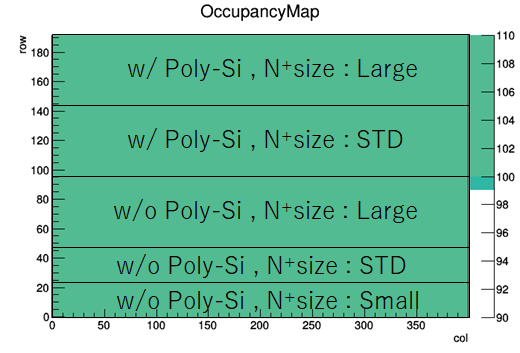

完成したmoduleの試験、sensorのtypeは以下の図の通り

| |

Sensor Type |

| Single1 |

|

| Single2 |

|

KEK53-3

direct modeでVDDD=1.23V , VDDA=1.20Vかけてconfig通る

digitalは良好、analogはsensorが付いている部分がきたない

LDO modeではそもそもconfigが通らない→LDOが壊れてる?

direct/LDO mode両方ともSTATUS信号は立ち上がらない(でもdirect modeでは動作する)

KEK53-4(STD)

direct modeでVDDD=1.21V , VDDA=1.20Vかけてconfig通る

しかし、digitalの結果が汚い(GNDの問題?)、analogはまだ

LDO modeでVDDD=1.87V , VDDA=1.87Vかけてconfig通る

だいぶ不安定(?)みたいで1.89Vぐらいかけないと通らないこともある(高めの電圧でconfigが通せると標準ぐらいの電圧でもある程度の時間configが通るようになる?)

こちらのdigitalは割ときれい(縦にポツポツと点線が現れるくらい)、analogは現状なにも返ってこない空っぽ

digitalがうまく返ってこないのはどうやらGND問題みたい←というのも、PORピンのGNDにpico太郎プローバーのGNDを付けるとうまく返ってくる

recommendationで取り外したR57のジャンパーを付けると直る?→変わらなかった

digitalがきれいに返ってきたのでanalog scanとThreshold scan(lin,diff)を実行

[6/18追記]

lin_thresholdを行うと途中でconfigが崩れてdig/anaがなにも返ってこない→dig currentによるものか

現状電源の入れ直しでのみ解消される

USBpixのregualtorで動かしてみる

VDDD=1.80V , VDDA=1.81Vで動作 KEK53-3と比べるとPORの立ち上がりが遅い?(要検証)

"LinKrumCurr"(Krummenacher(←読めない) feedbuck bias current)を50→4にするとAnalog応答のなかった部分が復活(4より下げると問題のなかった下部分の応答が悪くなっていく)

しかし、lin FEの上半分右で無応答の箇所が出てくる

"LinFcBias"(Folded cascode branch current)を20→150にすると無応答箇所周りの応答が少ない部分が減る?(なくなるわけではない)

[12/13追記]

direct : VDDD=1.20V, VDDA=1.20Vで動作

LDO :

VinD =1.80V,

VinA =1.80Vで動作

KEK53-5(STD, irrad)

LDO modeでVinD=1.87V , VinA =1.87Vでconfig通る

前2つのmoduleと同じようにPORピンのGNDにpicoプローバーのGNDを付けるとdigitalが返ってくるが、きれいにならない

config通った後のdig currentが2つと比べて高い(0.2Aのところが0.31Aほどになっている)←digitalが汚い原因?

digital scanが終わるとdig currentが0.53A程まで上がり、digital/analog scanがなにも返ってこなくなる←KEK53-3,4と比べて発生確率が高い

[7/25追記]

cyric照射準備時に移動boxかなんかに挟んでしまい、SCCが少し曲がってしまった

chipが割れた(外目からは割れてなさそう) or WBが導通したかでdirect modeでanalog currentがconfig通す前で~0.7A程かかるようになってしまったため現状なにもできない状態

一応照射はして、KEKに戻ってからワイヤーを打ち直してみる予定。。。

[9/6追記]

照射後測定

LDO modeでは動かなく、direct modeでVDDD=1.20V, VDDA=1.20Vを印加してconfig通る

diffは1200eまでtuningできることを確認

KEK53-6(Small Al)

LDO/dilectそのままでは応答はあるが、そのままでは汚いdigital scan結果が得られた。dilectでVDDD=1.23V , VDDA=1.20Vでscanを行うとうまく返ってこない。そこでVDDA=1.17Vにしたところdigital/analogともにきれいにかえってきた。

LDO(VinD=1.80V , VinA=1.80V)においては、config上でSoldAnalogTrimの値を26->16に変更。VDDAの値は1.3V->1.15Vとなった。

1.17Vに近づけるために26->16->19にすると1.178Vとなり、LDOでもdigital/analogが返ってくるようになる。

[12/13追記]

direct : VDDD=1.23V, VDDA=1.23Vで動作

LDO :

VinD =1.80V,

VinA =1.80Vで動作

KEK53-7(25x100um)

LDO mode 問題なく返ってくる。VDDA=1.3Vと高め。試しにSldoAnalogTrim26->19にしたところ、返ってくるdigital/analogは汚い。VDDAを下げてよくなるのは全部というわけではなさそう。

[9/10追記]

LDO modeで動かそうとするとVinA側がcurrent limitに引っかかり(>1A流れる)1.8Vかけることができない

direct modeだとVDDD=1.30V, VDDA=1.30Vかけてもconfig通らず

[12/13追記]

基本的に同上

direct : VDDD=1.30V, VDDA=1.30Vまでかけても動作させず VDDD=1.20Vでdigital currentが0.475A(通常は~0.1A)で高い

LDO :

VinA =1.80Vかけようとするとcurrent limit(>1A)で1.68Vしかかからない

[2019/10/30追記]

direct: VDDD=1.20V, VDDA=1.20V, current limit=3.5A で動作するがdigitalscanのOccupancy Mapは0、analogscanのOccupancy Mapはnoisyが数pixel

KEK53-8(25x100um, irrad)

LDO modeのdefault configのままではdigital/analog返らず。SldoAnalogTrimの値を26->19に変更したところthreshold scanまで返ってきた。VDDAをテスターで測ったところ1.17V

KEK53-9(thick SiO2 between Poly-Si & Al)

LDO modeではconfigは通らず。dilect modeにしたところ、configは通るが、digitalの分布は汚い。VDDD=1.23V , VDDA=1.20V->VDDD=1.23V , VDDA=1.17Vにしたところ、綺麗になりthresholdまで可能に。

[12/13追記]

direct : VDDD=1.30Vでdigital currentが0.008Aしか流れておらず、動作しない

LDO :

VinD =1.98V,

VinA =1.98Vで動作する、印加電圧がかなり高い

direct, LDOともに接触の問題か?

[4/4追記]

LDO :VinD = 2.0V,

VinA = 2.0VでSLDOをdig,anaともに20にして動作

Analog scanが少し汚い

KEK53-10(thick SiO2 under BR, irrad)

LDO modeのdefault configのままではdigital/analog返らず。SldoAnalogTrimの値を26->19に変更したところthreshold scanまで返ってきた。

KEK53-11(thick SiO2 under BR)

LDO modeではconfigは通らず。dilect modeにしたところ、configは通るが、digitalの分布は汚い。VDDD=1.23V , VDDA=1.20V->VDDD=1.23V , VDDA=1.17Vにしたところ、綺麗になりthresholdまで可能に。

[9/10追記]

LDO modeでconfig通らず

[12/13追記]

direct : VDDD=1.23V, VDDA=1.23Vで動作

LDO : 2.0Vまで上げても動作せず

[2019/10/30追記]

direct: VDDD=1.20V, VDDA=1.20V, current=1.1A でscanは走るがno data

KEK53-12(Poly-Si : 0.67MΩ/pixel)

LDO modeで問題なく返ってくる。regulator後のVDDAは1.37Vと高め。試しにSldoAnalogTrim26->19にしたところ、返ってくるdigital/analogは汚い。VDDAを下げてよくなるのは全部というわけではなさそう。

[12/13追記]

HVがshortしかかっている(保護抵抗が見えているわけではないので完全にはshortしていない)

direct : 1.30Vまでかけても動作せず

LDO : 2.00Vまでかけても動作せず

[2019/10/30追記]

direct, LDO 共に動作せず

KEK53-13(Poly-Si : 6MΩ/pixel, irrad)

LDO modeで問題なく返ってくる。regulator後のVDDAは1.3Vと高め。試しにSldoAnalogTrim26->19にしたところ、返ってくるdigital/analogは汚い。VDDAを下げてよくなるのは全部というわけではなさそう。

KEK53-14(Small Al, thick SiO2 btw PolySi-Al, Poly-Si : 6MΩ/pixel)

LDO modeでVinD=1.80V, VinA=1.80Vでconfig通る

デフォルトのconfigだとLin FEの応答がほとんど無い

[12/13追記]

direct : VDDD=1.30V, VDDA=1.30Vで動作するがnoisy

LDO :

VinD =1.80V,

VinA =1.80Vで動作

[4/4追記]

Digitalのレギュレータが動作不良

1.80Vをかけるとoutputが1.5Vくらいになるためdirectで測定。

[2020/2/16]

Direct Mode -> 1.30V

KEK53-15(Small Al, thick SiO2 btw PolySi-Al, Poly-Si : 6MΩ/pixel, irrad)

LDO modeではconfigが通らず、direct modeでVDDD=1.20V, VDDA=1.20Vにするとconfigが通るようになる

デフォルトのconfigだとLin FEの応答がほとんど無い

->HV-50VかけてAnalogscanとると全FE綺麗に返ってくる

KEK53-16(Small Al, Poly-Si : 6MΩ/pixel)

Direct, LDO modeともにLVショート

KEK53-17(Small Al, Poly-Si : 6MΩ/pixel, irrad)

Sync & Lin FEs disable

SyncとLin FEからのノイズがdiff FEのノイズに影響しないように電源を切る

EnableCoreColSync (Lin1, Lin2)を0に、Col : 0~263のEnableを0にするとdisableになる?

| |

|

All FEs |

Diff only |

| config前 |

Analog |

0.422 A |

0.423 A |

| Digital |

0.127 A |

0.127 A |

| config後 |

Analog |

0.262 A |

0.256 A |

| Digital |

0.298 A |

0.164 A |

digital currentは下がっているが、analog currentが下がっておらずちゃんとdisableできてない?→どうやらconfig fileでは完全にはdisableできないらしい

Sync FEに関しては"SyncAutoZero"をenableにするとFE disableにできる?

→configs/scans/rd53a内のconfig fileにある"globalpulseRT"を0にするか、configs/controller内のspecCfg.jsonにある"AZ word"を0にするとautozeroがdisableになる模様(未確認)

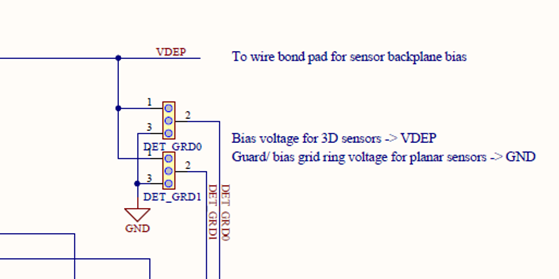

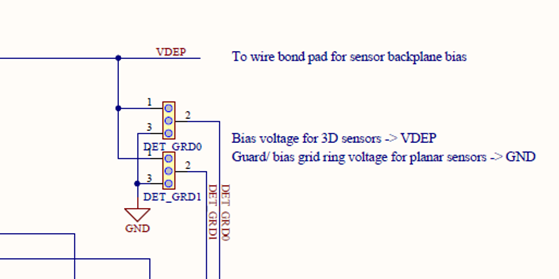

bias railをGNDに落とす

下図のDET_GRD0, 1とGNDをジャンパー接続することでbias railをSCCのGNDに落とすことができる

--

Atlasj Silicon - 2018-06-01

Atlasj Silicon - 2018-06-01

Comments

--

--