# **The RD53A Integrated Circuit**

ABSTRACT: Implementation details for the RD53A pixel readout integrated circuit designed by the RD53 Collaboration. This is a companion to the specifications document and will eventually become a reference for chip users. RD53A is not intended to be a final production IC for use in an experiment, and contains design variations for testing purposes, making the pixel matrix non-uniform. The chip size is 20.0 mm by 11.8 mm.

5

## Contents

|    | 1. | Intro                      | 3                                                  |    |  |

|----|----|----------------------------|----------------------------------------------------|----|--|

|    | 2. | Floorplan and Organization |                                                    |    |  |

|    | 3. | Power Distribution         |                                                    |    |  |

| 10 |    | 3.1                        | ShuLDO Voltage Regulators                          | 8  |  |

|    |    | 3.2                        | Power and Ground Network and Substrate Isolation   | 10 |  |

|    |    | 3.3                        | ESD Protection and Safe Wire Bonding               | 10 |  |

|    |    | 3.4                        | Load Model of RD53A for Serial Power System Design | 11 |  |

|    | 4. | Bun                        | np Pads, Wire Bond Pads, and Alignment Crosses.    | 14 |  |

| 15 |    | 4.1                        | Sensor Guard/Bias Ring Bumps                       | 15 |  |

|    | 5. | Ana                        | log Front Ends                                     | 17 |  |

|    |    | 5.1                        | Linear Front End Design                            | 17 |  |

|    |    | 5.2                        | Differential Front End Design                      | 20 |  |

|    |    | 5.3                        | Synchronous Front End Design                       | 21 |  |

| 20 |    | 5.4                        | Calibration Injection Circuit                      | 23 |  |

|    |    |                            | 5.4.1 Generation of S0 and S1 signals              | 24 |  |

|    |    | 5.5                        | Analog Bias                                        | 25 |  |

|    | 6. | Digi                       | tal Matrix                                         | 27 |  |

|    |    | 6.1                        | Distributed Buffer Architecture (DBA)              | 28 |  |

| 25 |    | 6.2                        | Central Buffer Architecture (CBA)                  | 30 |  |

|    |    | 6.3                        | Hit OR                                             | 31 |  |

|    | 7. | Digi                       | tal Bottom of Chip and Clocks                      | 32 |  |

|    |    | 7.1                        | Clocks and CDR/PLL                                 | 32 |  |

|    |    | 7.2                        | Start Up and Reset                                 | 34 |  |

| 30 |    | 7.3                        | JTAG and Command Bypass                            | 36 |  |

|    |    | 7.4                        | Trigger                                            | 37 |  |

|    |    | 7.5                        | Global Registers                                   | 37 |  |

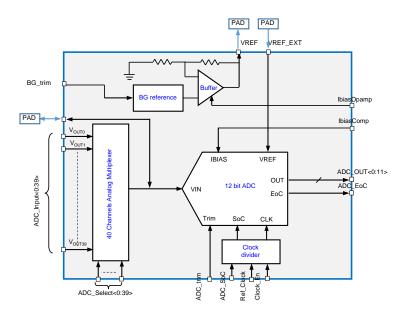

|    | 8. | Ana                        | 39                                                 |    |  |

|    |    | 8.1                        | Monitoring Block                                   | 39 |  |

| 35 |    |                            | 8.1.1 Analog Multiplexer                           | 40 |  |

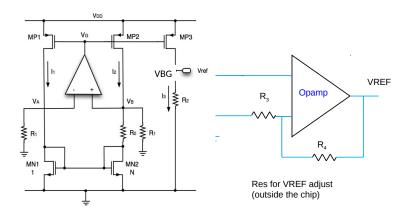

|    |    |                            | 8.1.2 Bandgap Reference                            | 40 |  |

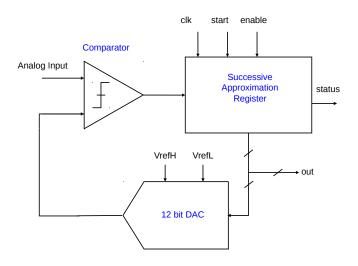

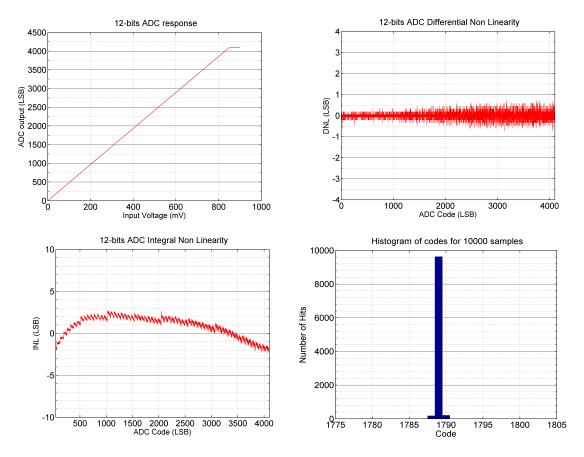

|    |    |                            | 8.1.3 SAR ADC                                      | 41 |  |

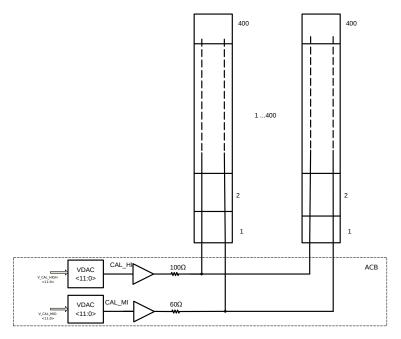

|    |    | 8.2                        | Calibration Injection Voltages                     | 42 |  |

|    | 9.  | Inp  | ut, Output and Configuration                | 44 |

|----|-----|------|---------------------------------------------|----|

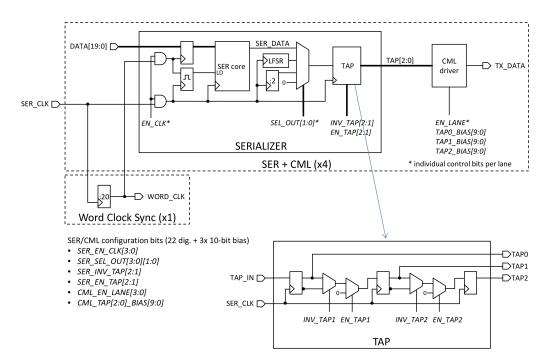

| 40 |     | 9.1  | 1.28 Gbps Output Serializer                 | 44 |

|    |     | 9.2  | Command Protocol                            | 45 |

|    |     |      | 9.2.1 Command Protocol Initialization       | 49 |

|    |     |      | 9.2.2 Command Protocol Transmission         | 50 |

|    |     |      | 9.2.3 Command Protocol Decoding             | 51 |

| 45 |     |      | 9.2.4 Command Protocol Timing               | 51 |

|    |     | 9.3  | Pixel Configuration                         | 52 |

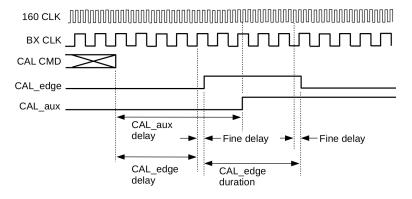

|    |     | 9.4  | Data Output Protocol                        | 54 |

|    | 10. | Test | t Features and Miscellaneous Functions      | 57 |

|    |     | 10.1 | Heartbeat and Fixed Output Patterns         | 57 |

| 50 |     | 10.2 | Alternate Readout                           | 57 |

|    |     |      | Boundary Scan                               | 57 |

|    |     |      | General Purpose LVDS Outputs and Hit-OR     | 57 |

|    |     |      | Analog Muxes                                | 57 |

|    |     |      | ADC-based Temperature and Radiation Sensors | 57 |

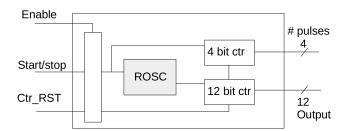

| 55 |     |      | Ring Oscillators                            | 58 |

|    |     |      | Top Pads and Pixel Outputs                  | 58 |

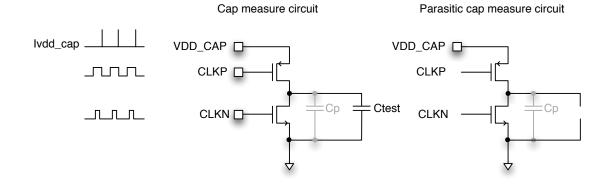

|    |     | 10.9 | Capacitance Measurement Circuits            | 59 |

|    | 11. | Ref  | erence Tables                               | 61 |

|    |     | 11.1 | Bottom Pinout                               | 61 |

| 60 |     |      | Top Pinout                                  | 64 |

|    |     |      | Global Register Assignments                 | 66 |

|    |     | 11.4 | Notes on Specific Registers                 | 69 |

|    |     |      | 11.4.1 CAL_COLPR_X                          | 69 |

|    |     |      | 11.4.2 GLOBAL_PULSE_RT                      | 69 |

| 65 |     |      | 11.4.3 OUTPUT_CONFIG                        | 69 |

|    |     |      | 11.4.4 OUT_PAD_CONFIG                       | 69 |

|    |     |      | 11.4.5 GP_LVDS_ROUTE                        | 70 |

|    |     |      | 11.4.6 CDR_CONFIG                           | 70 |

|    |     |      | 11.4.7 MONITOR_MUX                          | 70 |

| 70 |     |      | 11.4.8 SENSOR_CONFIG                        | 71 |

|    |     |      | 11.4.9 RING_OSC                             | 71 |

|    |     | 11.5 | 11.4.10 FIFO Full Counters                  | 72 |

|    |     | 11.5 |                                             | 72 |

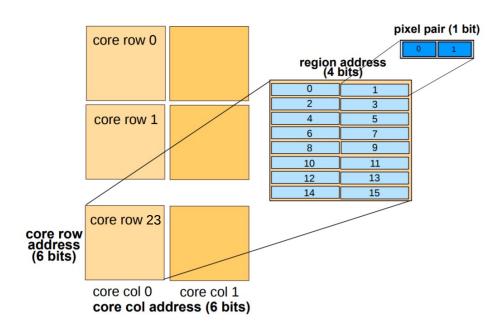

|    |     | 11.6 | Pixel Addressing                            | 72 |

| 75 | A.  | Rad  | liation Tolerance                           | 74 |

|    |     | A.1  | Total Ionizing Dose                         | 74 |

|    |     | A.2  | Single Event Upsets                         | 74 |

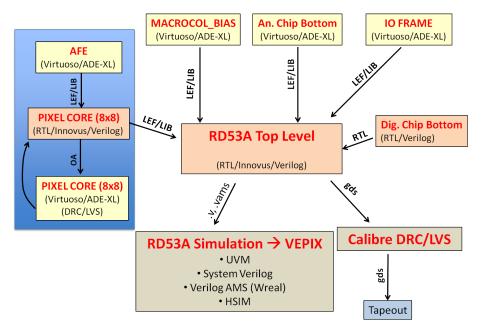

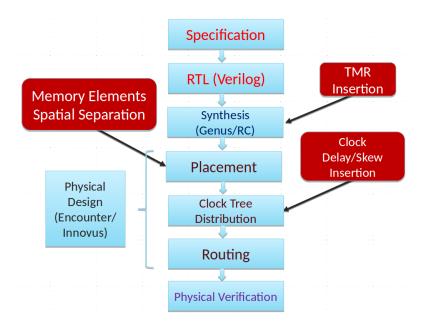

|    | В.  | Met  | thodology and Design Flow                   | 76 |

|    | С. | Peculiarities ("Quirks") of the RD53A Design |                                                            |    |

|----|----|----------------------------------------------|------------------------------------------------------------|----|

| 80 |    | C.1                                          | Current Reference Trim Bits                                | 77 |

|    |    | C.2                                          | Distribution of Calibration Edge                           | 77 |

|    |    | C.3                                          | Charge Injection from Priming                              | 77 |

|    |    | C.4                                          | Empty Packets in Single Lane AURORA with Saturated Readout | 77 |

|    |    |                                              |                                                            |    |

#### 1. Introduction

The RD53A integrated circuit specifications [1] were approved in Fall 2015 after review by the AT-LAS, CMS, and RD53 collaborations. Chip design to meet these specifications began in 2016. This document describes the design and implementation choices and is expected to eventually become a chip users' guide. RD53A is intended to demonstrate in a large format IC the suitability of the chosen 65nm CMOS technology for HL-LHC upgrades of ATLAS and CMS, including radiation tolerance (Sec. A), stable low threshold operation, and high hit and trigger rate capabilities. RD53A is not intended to be a final production IC for use by the experiments, and will contain design variations for testing purposes, making the pixel matrix non-uniform (Sec. 5). It will form the basis for the production designs of ATLAS and CMS. The design revisions from RD53A to production will involve selecting one of the front end variants and uniformly using it everywhere, increasing the pixel matrix size as specified by each experiment, and tailoring the digital functionality to according to the experiment specifications. These should all be achieved by changing parameters and high level description code and re-running the RD53A design flow, which is developed with such flexibility in mind (App. B). RD53A will be fabricated on an engineering wafer run shared with the CMS MPA chip in order to control prototyping cost.

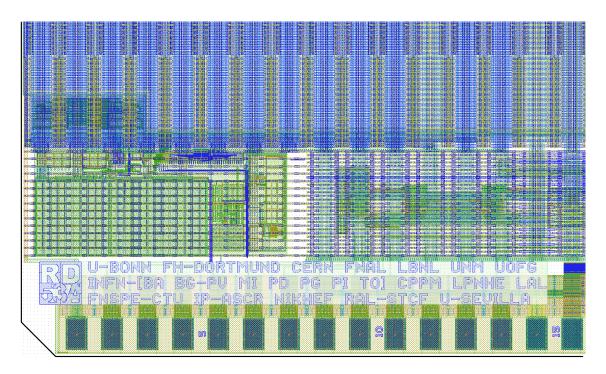

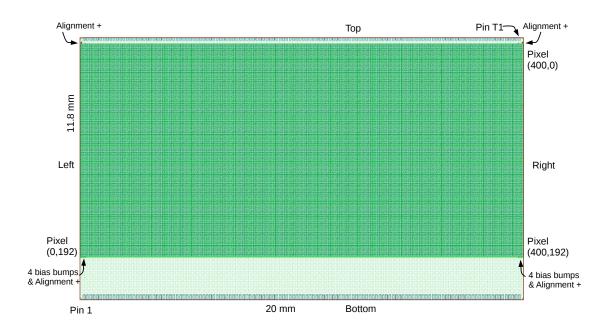

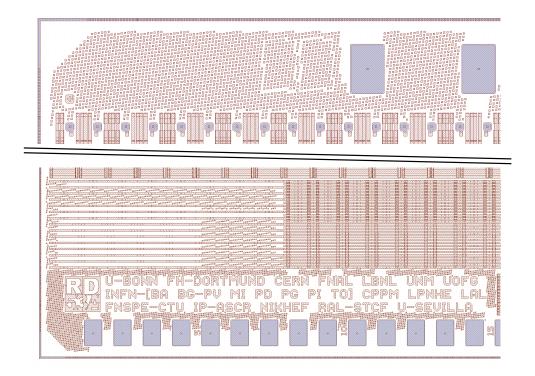

The physical size and pad locations are shown in Fig 1. Sec. 4 describes the pads in detail. The width of RD53A is 20 mm, as it expected that the final production chips will be 20 mm or wider and can therefore reuse the bottom of chip and pad frame. The height of the RD53A chip is constrained by available space on the shared reticle submission. The RD53A pixel matrix is 400 pixels wide by 192 pixel tall. Production chips are expected to increase the number of rows and remove the top row of test pads. The power and bias distribution have been designed for a larger number of rows, up to 384. The labels top, bottom, left, and right refer to the orientation as shown in Fig 1. (For pixel numbering see Sec. 11.6). Alignment crosses are included on the top left and right sides, while at the bottom there are small crosses (the size of one bump bond pad) described in Sec. 4.

**Figure 1:** Top view of RD53A layout. The width is 20mm and 400 pixels, and the height is 11.8mm and 192 pixels.

#### 2. Floorplan and Organization

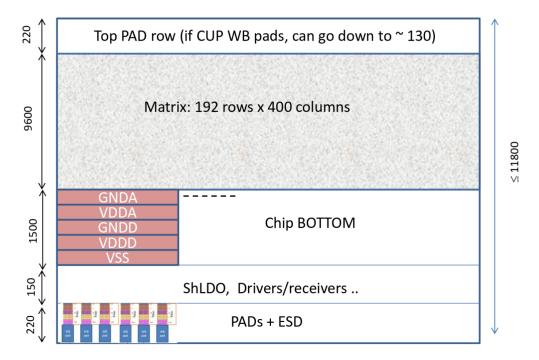

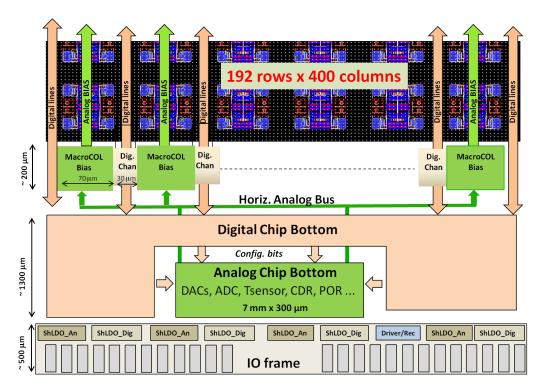

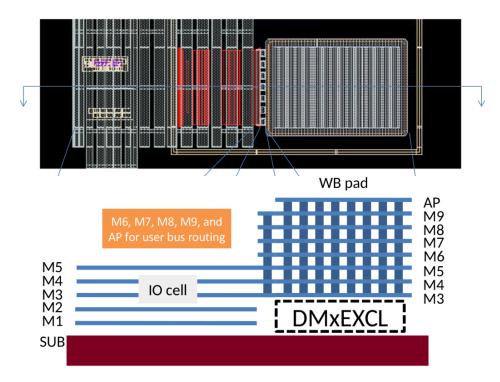

RD53A uses a 9 metal layer stack, consisting of 7 thin, 1 thick and 1 ultra-thick metal layers. In addition, the 28K AP layer is also used for power lines distribution. In Fig. 2 and Fig. 3 the layout and functional view of RD53A floorplan are shown. The sensitive area of the chip is placed at the top of the chip and is arranged as a matrix of 192 x 400 pixels of  $50 \,\mu\text{m} \times 50 \,\mu\text{m}$ . At the top is a row of test pads for debugging purposes, which should be removed in a production chip. The peripheral circuitry is placed at the bottom of the chip and contains all global analog and digital circuitry needed to bias, configure, monitor and readout the chip. The wire bonding pads are organized as a single row at the bottom chip edge and are separated from the first row of bumps by 1.7 mm in order to allow for wire bonding after sensor flip-chip (Sec. 4). However, the wire bond pads are also designed compatible with Thru-Silicon Via post processing.

Figure 2: RD53A floorplan, layout view.

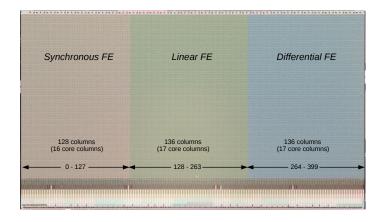

The pixel matrix is built up of 8 by 8 pixel *cores*. The 64 front ends within a core are placed as 16 so-called analog islands with 4 fronts ends each, which are embedded in a flat digital synthesized "sea" as shown in Fig. 4. The circuitry around each island is not identical but depends on the placement of gates by the synthesis tool. Prototype tests have shown that, within the digital/analog isolation scheme used, this approach does not introduce any visible systematic differences between islands. Furthermore, a core is small enough that it can be checked with a transistor level analog simulation. In the chip periphery, all the analog building blocks are grouped in a macroblock called Analog Chip Bottom (ACB), which is fully assembled and characterized in an analog environment (Sec. 8). All the building blocks have been previously prototyped, tested and characterized in radiation environment at least up to 500 Mrad TID. The ACB block is surrounded by a synthesized

Figure 3: RD53A floorplan, functional view.

block, called Digital Chip Bottom (DCB), which implements the Input, Output and Configuration digital logic, as described in (Sec. 7) and (Sec. 9).

Figure 4: Layout of analog island concept.

#### 3. Power Distribution

150

RD53A is designed for single supply serial powered operation with connections from the bottom of chip only. However, because it is a prototype that must have flexibility for a variety of measurements, it is also be possible to power the chip by directly supplying the internal rail voltages, bypassing the regulation. There are two internal voltage rails for powering the chip core, analog (VDDA) and digital (VDDD). In addition, two blocks (serializer/CML cable driver and PLL) have their individual power pads: VDD\_CML/GND\_CML and VDD\_PLL/GND\_PLL, respectively. User must texternally connect these power pins to one of the two rails. This was done to allow testing of power sensitivity of these circuits. The ESD protection scheme uses additional rails as discussed in Sec. 3.3. The separation between local analog ground, digital ground, and substrate is discussed in Sec. 3.2. The operation of a serial powered detector is new, and system design requires a simplified load module of the chip to understand how to design the power distribution and cooling and how the system responds to transients, faults, etc. Such a model is given in Sec. 3.4. The chip has a Power On Reset (POR) covered in Sec. 7.2. When power is applied it should be ramped up fasteer than the POR delay for proper reset: this delay is nominally 50 ms. Table 1 gives the power supply limits.

| Parameter                              | Typ.      | Max.   |

|----------------------------------------|-----------|--------|

| Core direct supply voltage             | 1.2 V     | 1.32 V |

| ShuLDO input voltage                   | 1.5 V     | 2.0 V  |

| Per pixel analog current               | $4 \mu A$ | 8 μΑ   |

| Per pixel digital current              | 4 μΑ      | 6μΑ    |

| RD53A Periphery analog current         | 30 mA     | 60 mA  |

| RD53A Periphery digital current        | 30 mA     | 60 mA  |

| Output drivers (each)                  | 20 mA     | 30 mA  |

| Total RD53A current (4 outputs)        | 0.75 A    | 1.3 A  |

| 400x384 chip periphery analog current  | 30 mA     | 60 mA  |

| 400x384 chip periphery digital current | 60 mA     | 120 mA |

| Total 400x384 chip current (4 outputs) | 1.3 A     | 2.3 A  |

**Table 1:** Power supply limits

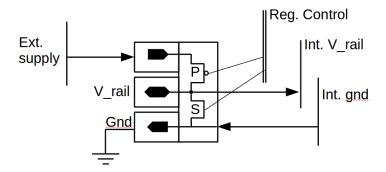

To meet the above needs, RD53A uses "active power pads" as shown in Fig. 5. The pad has an active mode and a passive mode. The passive mode is activated by tying the external supply and the V\_rail pins together and disabling the Shunt transistor, in which case the user externally controls the corresponding internal voltage rail. In the active mode the V\_rail pin can be used to connect external decoupling capacitors, but no DC current flows on it. Special voltage regulators called ShuLDOs (short for Shunt-LDO) are used. The ShuLDO control circuit ensures that the external supply pad sinks a constant input current independent of the internal circuit consumption, and generates a regulated output voltage (V\_rail) to the chip interior. The voltage rail (ShuLDO output) can be adjusted through the chip configuration (Table 24). The ShuLDO control circuit is common to all the power pads feeding the same rail and is described in Sec. 3.1. Any excess current

**Figure 5:** Active power pad as described in the text. The labels P and S stand for Pass and Shunt transistors, which are actively controlled by the ShuLDO regulator circuit.

not needed by the chip internal circuits is shunted to ground, with the sum of chip core and shunt currents remaining constant. Use of a common control circuit permits having multiple active pads in parallel, distributed along the chip bottom. This avoids having a single power device (regulator) where all the current for a given rail must be concentrated, which would present reliability challenges. The shunted current to ground will be evenly distributed among all the parallel active pads, as this is a feature of the ShuLDO design. The chip contains two ShuLDO control circuits, one for the analog and another for the digital internal rails, and 4 active pads associated with each. As the absolute maximum current consumption of a full size (400 pixels by 384 pixels) chip would be 1.5 A each analog and digital, this means that each active pad must be rated for 375 mA plus some derating for current sharing and failures. Each active pad has therefore been designed for 500 mA maximum current, and assigned 5 input and 5 ground wire bonding pads. The absolute maximum current rating for the full chip is therefore 4.0 A.

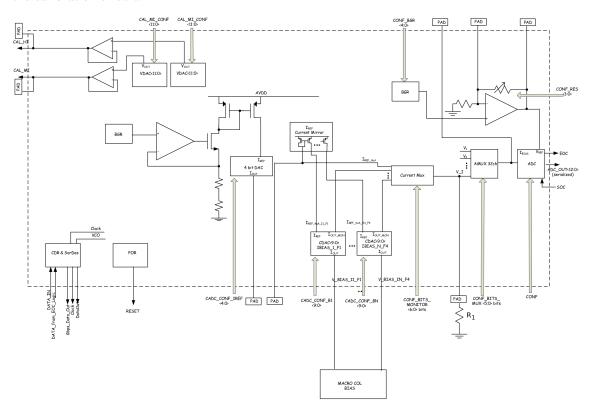

#### 3.1 ShuLDO Voltage Regulators

180

The Shunt-LDO regulator (ShuLDO) is a combination of a low-drop linear voltage regulator and a shunt regulator. The regulator can be configured as a pure Low Drop-Out linear voltage regulator for usage in a conventional voltage based supply scheme. In addition, the regulator provides dedicated shunt circuitry which can be enabled for application in a current based serially powered supply scheme. The power device of each regulator, namely the pass, and the shunt device, are each split into four parts and spread across the pad frame to balance power distribution, but there is a single control circuit per regulator.

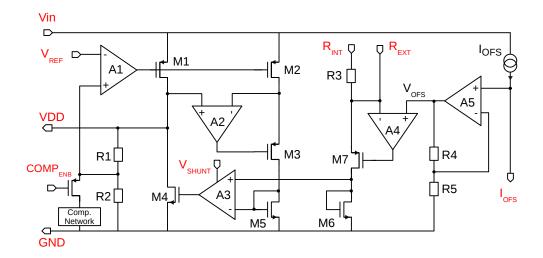

A simplified circuit of the Shunt-LDO regulator is shown in Fig. 6 and the inputs and outputs are listed in Table 2. The LDO regulator part is formed by the error amplifier A1, the PMOS pass transistor M1 and the voltage divider formed by the resistors R1 and R2. In a voltage based supply scheme, the unregulated input voltage is applied to the  $V_{IN}$  pin while GND corresponds to local ground. The regulator generates an output voltage VDD=2 ×  $V_{REF}$  where  $V_{REF}$  is the reference voltage which is provided to the inverting input of the error amplifier A1.

In a constant current scheme the supply current is flowing into the V<sub>IN</sub> pin. The pass transistor

Figure 6: LDO regulator with shunt capability (Shunt-LDO)

| Pin                 | Type    | Min.   | Тур.            | Max.   | Description                                |

|---------------------|---------|--------|-----------------|--------|--------------------------------------------|

| V <sub>IN</sub>     | Power   | 1.4 V  |                 | 2.0 V  | external power input (voltage)             |

|                     | Power   | 0      | 0.5 A           | 2.0 A  | external power input (current)             |

| $V_{SHUNT}$         | Power   | 1.4 V  |                 | 2.0 V  | supply voltage of shunt circuitry          |

| GND                 | Ground  |        |                 |        | local ground and shunt current output      |

| VDD                 | Power   | 1.0 V  | 1.2 V           | 1.32 V | regulator output                           |

| $V_{REF}$           | Analog  | 500 mV | 600 mV          | 660 mV | reference voltage (VDD=2V <sub>REF</sub> ) |

| R <sub>INT</sub>    | Analog  |        | V <sub>IN</sub> |        | supply/enable internal ref. R              |

| R <sub>EXT</sub>    | Analog  | 300 Ω  |                 |        | external ref. R to V <sub>IN</sub>         |

| I <sub>OFS</sub>    | Analog  |        | 200 kΩ          |        | external offset R to GND                   |

| COMP <sub>ENB</sub> | Digital |        | GND             |        | GND to enable compensation                 |

Table 2: Shunt-LDO regulator circuit pins

M1 is steered to create a voltage drop  $V_{DS}$  between the regulator input  $V_{IN}$  and the output voltage terminal, VDD, such that the desired output voltage is generated with respect to local ground. The shunt transistor M4 is added to provide an additional current path to GND: it is controlled to drain all current which is not drawn by the load connected to VDD. For this purpose the current flow through transistor M1 is compared with a reference current which is defined by use of resistor R3, amplifier A4 and transistor M7. Due to the negative feedback loop, the amplifier A4 is applying the offset voltage  $V_{OFS}$  to the lower terminal of resistor R3, while the  $V_{IN}$  potential is connected to the upper terminal. If the voltage at the  $V_{IN}$  terminal is higher than the offset voltage  $V_{OFS}$ , the reference current is flowing through resistor R3 and given by:

$$I_{ref} = \frac{V_{IN} - V_{OFS}}{R3} \tag{3.1}$$

If the voltage at the  $V_{IN}$  terminal is lower than the offset voltage  $V_{OFS}$ , the reference current equals

to zero. While the reference current is drained into the gate-drain connected transistor M6, a fraction of the current flowing through transistor M1 given by the aspect ratio k of the current mirror formed by transistor M1 and M2, is drained into the gate-drain connected transistor M5. The value of k is 1000 and thus the total current in shunt mode is 1000 times the reference current. The amplifier A2 and the cascode transistor M3 are added to improve the mirroring accuracy. The reference current is compared to the fraction of current flowing through transistor M1 by use of the differential amplifier A3. If the current drained to transistor M6 is smaller than the reference current, the shunt transistor M4 is steered to draw more current and vice versa. By this means, a constant current independent of the regulator load is flowing through transistor M1 with a value defined by:

$I_{IN} = k \frac{V_{IN} - V_{OFS}}{R3} \tag{3.2}$

The resistor R3 is integrated internally and has a design resistance of  $600\,\Omega$ . R3 sets the reference current if  $R_{INT}$  is connected externally to  $V_{IN}$ . However the reference current can be set to any desired value by using an external resistor instead to R3, placed between  $R_{EXT}$  and  $V_{IN}$ . In this case  $R_{INT}$  is kept floating (or if it is not then the external and internal resistors add in parallel). Note that for a reasonable offset voltage of around 1 V the total current set by R3 will be fairly large:  $667\,\text{mA}$  at  $V_{IN}$ =1.4 V, which significantly exceeds the RD53A nominal analog or digital current, and is instead of the order of a full chip analog or digital current. Therefore, for efficient RD53A operation  $R_{EXT}$  should be used instead of  $R_{INT}$  (alternatively a series resistor can be added on  $R_{INT}$  and  $R_{EXT}$  can be left unconnected).

For the generation of the offset voltage  $V_{OFS}$ , the bias current  $I_{OFS}$  of  $2\,\mu A$  is drained to an external resistor which is connected between the  $I_{OFS}$  pin and ground. The voltage is amplified by factor two by the non-inverting amplifier A5 and fed to A4. The generated offset voltage is  $V_{OFS} = 2I_{OFS}R_{OFS}$ , where  $R_{OFS}$  is the external resistor connected to the  $I_{OFS}$  pin.

A compensation circuit for stable operation of the regulator circuit with low ESR output capacitors is enabled by the digital port  $COMP_{ENB}$ , which is active low. This circuit should be used  $(COMP_{ENB})$  for normal operation. Shunt operation is disabled by shorting the Rext and VDDShunt ports to the local ground port GND. The amplifier A3 has a dedicated power pin,  $V_{SHUNT}$ , so that the shunt transistor M4 can be completely off in case of using passive mode of the power pins to directly control the internal supply rails.

#### 3.2 Power and Ground Network and Substrate Isolation

Digital and Analog power and digital and analog return (ground) are independently distributed throughout the pixel matrix. The digital and analog grounds are expected to be connected together with low impedance off chip. The ESD rail force the connection of analog and digital grounds at a single point on-chip, in the wire bond pad frame (see Sec. 3.3).

All circuits (both analog and digital) have been placed in deep N-wells for maximum possible substrate isolation. The only exceptions are the ESD protection structures of the wire bond pads, as descried in Sec. 3.3.

#### 3.3 ESD Protection and Safe Wire Bonding

215

220

In the bottom pad frame the four power domains (VDDA, VDDD, VDD\_CML, and VDD\_PLL) are

isolated by power-cut cells. Within a power domain group, the IO pad ESD devices are connected to the respective power rails. To allow an ESD path between power domains a common ESD bus connects to every power domain's ground rail via sets of anti-parallel diodes. This ESD bus is also used to connect the global substrate of the chip (VSUB). Because the IO pads use ESD devices connecting to the power rails, care must be taken to not drive signals to the chip while it is not powered, as this would supply parasitic power. There are a few pads which have an overvoltage tolerant ESD protection without a current path to the power rail. These pads are used where the input voltage can exceed the VDDA/VDDD rail potentials (input- and bias pads of the shunt regulator blocks, for example). Where low capacitance is mandatory (CML driver output pads) a path to the VDDA/VDDD rails was also omitted.

The top test pads have an independent power domain (VDD\_TOP/GND\_TOP) which is not connected to the global ESD bus at the chip bottom. Within the top row the IO pads are protected but since there is no connection to the global ESD bus, ESD events between top and bottom pads should be avoided. The IO pads in the top pad frame are all over-voltage tolerant and therefore output signals are not clamped if the top row is not powered.

The wire bonding sequence to avoid ESD problems is as follows: Start with the VSUB pads (14, 88 and 184) followed by all GND pads in any order. Finally bond the remaining pads in any order. The top row pads can be left floating, but if wire bonded then start with the GND pads (T2, T51 and T97) followed by the VDD pads (T1, T50 and T96) and then all other pads.

#### 3.4 Load Model of RD53A for Serial Power System Design

275

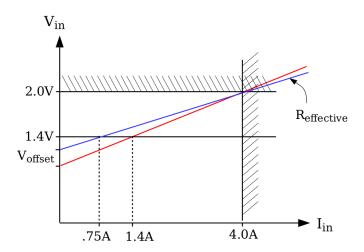

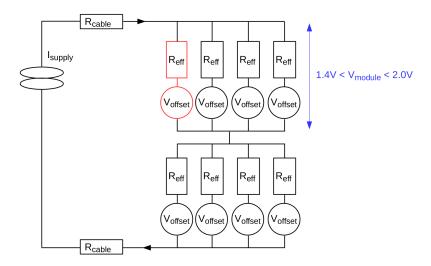

The ShuLDO regulator as seen by the external system can be modelled as an effective resistance,  $R_{\text{effective}}$ , in series with a voltage offset,  $V_{\text{offset}}$ . The internal chip core load is not directly visible to the external user. As shown in Fig. 7, the two parameters  $R_{\text{effective}}$  and  $V_{\text{offset}}$  can be typically chosen by considering two extreme operating points: the lowest and highest current and voltage, and connecting them by a straight line. The minimum voltage needed for regulation (1.4 V in the case of running with 1.2 V core voltage) should occur at the minimum required operating current, which is given by the current consumption of the chip core, without any additional current shunted in the regulators (Table 1. Clearly, at least this current must be supplied for the chip to work properly. For reliable operation the serial current supply setting will exceed this minimum current by some margin, and the module voltage will therefore be higher than 1.4 V according to the curve in Fig. 7. How much current margin to add on top of the core current (10%, 20%, etc.) is a user choice. Of course, the core current is also a user choice, as it is given by the selected analog biases, output modes and regulator output voltage settings. At the other extreme, the absolute maximum voltage should result from the the maximum current. Assuming a current higher than the absolute maximum will never be supplied, this guarantees that the absolute maximum voltage will never be exceeded. The comparison of these choices for RD53A and a full size chip is shown in Fig. 7. The effective resistance values in the figure are  $(2.0 \text{ V}-1.4 \text{ V})/(4.0 \text{ A}-0.75 \text{ A}) = 185 \text{ m}\Omega$  for RD53A and  $230 \,\mathrm{m}\Omega$  for a full-size chip. The slope is lower (less resistive) for RD53A because the offset voltage can be higher.

It should be clear from the above that the ShuLDO effective resistance  $R_{\text{effective}}$  is not the load resistance of the chip core (core current over core voltage). Because of the voltage offset, the power consumption also has a constant offset  $P = I_{\text{in}}^2 R_{\text{effective}} + I_{\text{in}} V_{\text{offset}}$ . A low value of ShuLDO  $R_{\text{effective}}$

**Figure 7:** Voltage vs. current behavior of chip load model. The shaded regions show the absolute maximum ratings: 2.0 V maximum voltage and 4.0 A per chip maximum current. The horizontal line at 1.4 V shows the minimum voltage needed for operation with 1.2 V regulated chip core voltage. The slopes represent the effective resistances of the RD53A chip (blue) and an expected full size chip (red), respectively. The dashed vertical lines at 0.75 A and 1.4 A are the nominal currents (not including shunt regulator margin) for the RD53A and expected full size chip.

is desirable because it leads to small change in power with supply current, and so a small regulation overhead. For RD53A, with  $R_{\rm effective}$ =185 m $\Omega$ , a 20% margin in the serial current results in a power overhead of 22%, while for a full size chip with  $R_{\rm effective}$ =230 m $\Omega$  a 20% current overhead results in a power overhead of 26%. It is also possible to purposely choose lower  $R_{\rm effective}$  values to reduce the power overhead. This is in fact also desirable to provide safety margin against faults as discussed below. However, non-zero value is needed for multiple regulators to work well in parallel, and there is furthermore a lower limit to the achievable  $R_{\rm effective}$  from transistor performance. the estimated lower limit per RD53A chip (8 regulators in parallel) is ???. With this value of  $R_{\rm effective}$  a 20% current overhead translates to a ???% power overhead.

In a serial powered system, several chips are wired in parallel within a module, and several modules in series, as shown in Fig. 8. It is instructive to work through an example of 8 modules in series with 4 full size chips per module. We start by assuming the above  $R_{\rm effective}$ =230 m $\Omega$  per chip and  $V_{\rm offset}$ =1.08 V. Thus at a current of 1.4 A per chip ( $I_{\rm supply}$ =5.6 A),  $V_{\rm module}$ =1.4 V. To have some operating margin, we set the serial current 20% higher,  $I_{\rm supply}$ =6.7 A. Now  $V_{\rm module}$ =1.47 V. The total chain voltage drop is 11.8 V because there are 8 modules. There is also resistance in the 100 m cable runs. Let us assume a 2  $\Omega$  round trip cable resistance, and so the power supply output voltage is 25 V. Note 50% of the supplied power is lost in the cables: while this may sound bad, it is an improvement over present pixel detectors. Just as we would set a current limit on constant voltage supplies, we set a voltage limit on serial power supplies, so we limit them at 27 V. The maximum power that can be delivered to the detector is thus 27 V×6.7 A minus the cable loss, or 11.5 W per module, while the operating power is 9.8 W per module.

Now suppose one chip in one modules fails (since each chip has two independent regulator controllers, the more probable scenario is for half of a chip to fail). Since the total current is sill the

**Figure 8:** Simple model of multi-chip modules in a serial power chain. The chip model in red is referred to in the text to discuss the impact of failures.

same (forced by the supply), each of the three remaining chips must pass a current of 6.7/3=2.23 A. Therefore  $V_{\text{module}}=1.6$  V. The power in this one module is now 10.7 W- a 9% increase. For the total 8-module chain power the increase is just 1%. The power supply output voltage will increase slightly to deliver the additional power, still well below the 27 V safety limit. In fact, even with 1 disabled chip in every module the supply will stay below the safety limit, since it is set to deliver up to 11.5 W per module. If 2 chips fail on a single module, then the per chip current is double the normal, 3.36 A, which is still below the absolute maximum rating of 4.0 A. The module voltage will be 1.85 V and the module power 12.4 W. While this is higher than the per module power supply limit, the full chain power remains well below the power supply limit and the system should continue to operate normally.

310

Finally we consider operation near the maximum ratings, should that be necessary. A single point failure "runaway" condition could be reached if the failure of one chip is able to trigger the failure of the rest of the module. In order to be safe against this scenario, the supply current must always be compatible with flowing through 3 chips instead of 4. Since the absolute maximum rated per chip current is 4 A, this means that the maximum safe supply current should be 12 A, which in a normal module translates to 3 A per chip. At this current, with our example  $R_{\rm effective}$  and  $V_{\rm offset}$ ,  $V_{\rm module}$ =1.77 V. The module power would thus be 21.2 W and the supply voltage, including cable drop, 38 V. If a chip then fails the module power rises to 24 W at  $V_{\rm module}$ =2 V.

#### 4. Bump Pads, Wire Bond Pads, and Alignment Crosses.

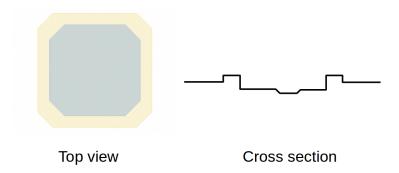

The bump pad shape and dimensions are shown in fig. 9. The passivation opening is square shape with 45 degree corners. The figure also shows the expected height profile across the center of a bump pad as derived from the metal stack.

**Figure 9:** Bump pad layout for RD53A (left) and expected surface profile (right). The dark central area of the layout is the passivation opening, which is  $12 \,\mu \text{m}$  wide, while the borders shows the pad metal extending an additional  $1.5 \,\mu \text{m}$  on all sides under the passivation. The exposed metal is not completely flat and can have depressions less than  $1 \,\mu \text{m}$  deep due to vias below. The profile shows such a depression.

The wire bond pads at the chip bottom are rectangular shape, with  $58 \,\mu\text{m}$  wide by  $86 \,\mu\text{m}$  tall passivation opening on a  $100 \,\mu\text{m}$  pitch (pinouts can be found in Sec. 11). This size is considered large enough to allow for wafer probing followed by reliable wire bonding with the possibility of bond repair. Only the bottom of chip pads need to be connected for normal operation. The top of the chip has test pads for dedicated measurements. The top test pads use the same layout but placed on a  $200 \,\mu\text{m}$  pitch. Figure 10 shows top and bottom layout details where the wire bond pads are visible. In the top left (right) corner there is a small alignment cross placed  $50 \,\mu\text{m}$  above the top left (right) bump pad. There are also alignment crosses at the bottom of the matrix shown in Sec. 4.1. In the bottom left corner is the RD53A logo listing the collaborating institutes.

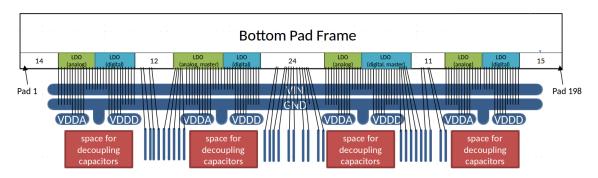

The bottom of chip pad layout is shown graphically in Fig. 11, including typical wire bond connections to as needed for realistic detector module operation (refer to Sec. 11 for pinout). There are four power groups, each with an analog and a digital Shunt-LDO regulator next to each other. The number of non-power wire bonds is small as only the serial control input and 1 to 4 high speed differential outputs are needed. A detail showing one bottom pad (oriented sideways) and ESD protection structures as well as the metal stack in each region, is showing in Fig. 12. Wire bond pads use most metal layers for compatibility with thru-silicon vias. The lowest two layers, M1 and M2 are excluded from the stack to avoid a high capacitance to the substrate, which would be problematic for high speed pads. This means TSV processing needs to drill through additional oxide to reach M3, which is considered an acceptable compromise. The bottom of chip pin assignments are given in Table 14 with pin 1 on the left side. The top test pin assignments are given in Table ?? with pin T1 on the left side.

**Figure 10:** Top metal and passivation layout details of top left and bottom left corners of RD53A. The magnification is different for top and bottom: the wire bond pads are all the same size, but the pitch is  $200 \,\mu\text{m}$  on at the top of the chip and  $100 \,\mu\text{m}$  at the bottom. In the top left an alignment cross is also visible which is placed  $50 \,\mu\text{m}$  above the top left bump pad. Metal fill (small peppered squares) is also visible.

**Figure 11:** Organization of bottom of chip pad frame. Typical wire bond connections needed for realistic detector module operation are also shown. The number of pads in each group is indicated.

#### 4.1 Sensor Guard/Bias Ring Bumps

Special bumps for access to sensor guard rings or bias grids will be included at the bottom of the regular bump matrix. These will be connected by metal, without antenna diodes, to dedicated wire bond pads. Note these are not rated to carry high voltage, but expected to be at near ground reference potentials. Four such special bumps at each end will be included as shown in Fig. 13. On each side of the chip, the group of four bumps is connected together to the first/last wire bond pad

Figure 12: Detail of wire bond pad, ESD structures, and metal stack.

350 (see Table 14).

**Figure 13:** Location of guard ring / bias grid bumps. The placement is equivalent to an extra bottom row, but only with the first 4 and last 4 columns populated. In the fifth location from both ends is a miniature alignment mark made of floating metal covered with passivation.

#### 5. Analog Front Ends

RD53A contains three different front end designs to allow detailed performance comparisons. These are not small variants of one common design, but substantially different ground-up designs. They are identified as Differential, Linear and Synchronous. The Differential front end uses a differential gain stage in front of the discriminator and implements a threshold by unbalancing the two branches. The Linear front end implements a linear pulse amplification in front of the discriminator, which compares the pulse to a threshold voltage. The Synchronous front end uses a baseline "auto-zeroing" scheme that requires periodic acquisition of a baseline instead of pixel-by-pixel threshold trimming. The designs are individually described in Sec. 5.1, 5.2, and 5.3, respectively. They share some common constraints and features, the main being the layout area and the bump bond pads, which are the same for all designs, making them easily interchangeable on the pixel matrix layout. The analog *quad* layout area is  $70 \,\mu\text{m}$  by  $70 \,\mu\text{m}$ , containing four front ends and four bump pads on a  $50 \,\mu\text{m}$  by  $50 \,\mu\text{m}$  grid. Also common to all front ends is the calibration injection circuit (Sec. 5.4), as this is important for direct performance comparisons. The bias distribution follows the same organization for all 3 flavors as described in Sec. 5.5.

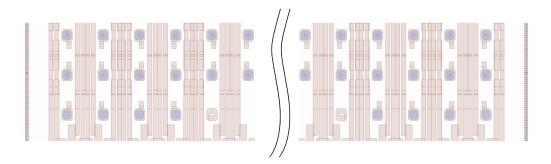

The front end designs share the pixel matrix area as shown in Fig. 14. It was not possible to have equal area for all designs because the 400-pixel wide matrix is built of  $8 \times 8$  pixel synthesized *cores*. Therefore two designs must have a 17 core width while one must have a 16 core width. The 16 core width was assigned to the Sync. FE flavor because it is simulated to use slightly more power. The Diff. and Lin. FE designs were placed next to each other because they have the most similar functionality, allowing for the largest possible area with uniform response, as desired for sensor characterization in test beams. They also are read out by the same digital region architecture, whereas the Sync. FE implements a different architecture (See Sec. 6). The output data format is the same for both readout architectures. The Diff. FE and Distributed Buffer (DB) region architecture have been prototyped in the FE65-P2  $64 \times 64$  pixel demonstrator, while the Lin. and Sync. FE and Central Buffer (CB) architecture have been prototyped in the Chipix  $64 \times 64$  pixel demonstrator.

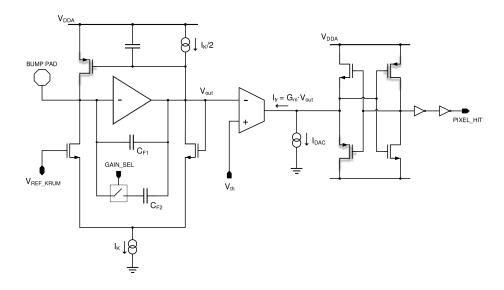

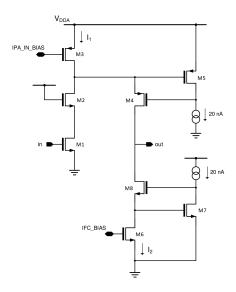

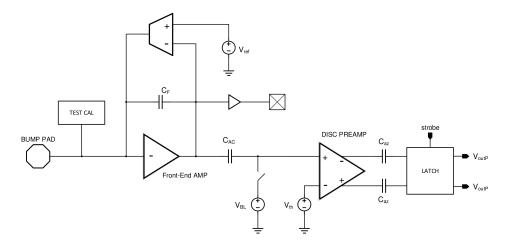

#### 5.1 Linear Front End Design

The Linear front-end is shown in figure 15. The readout chain includes a charge sensitive amplifier (CSA) featuring a Krummenacher feedback complying with the expected large radiation induced increase in the detector leakage current. The choice of a single amplification stage in the front-end channel has been simply dictated by power consumption and area constraints. The signal from the CSA is fed to a high-speed, low power current comparator that, combined with the time-over-threshold (ToT) counter, is exploited for time-to-digital conversion. Channel to channel dispersion of the threshold voltage is addressed by means of a local circuit for threshold adjustment, based on a 4-bit binary weighted DAC generating the current  $I_{DAC}$ . The front-end chain has been optimized for a maximum input charge equal to 30000 electrons and features an overall current consumption close to 4  $\mu$ A. The CSA can be operated in high gain (floating  $C_{F2}$ ) and low gain mode ( $C_{F1}$  in parallel with  $C_{F2}$ ) by acting on the GAIN\_SEL bit, whereas the recovery current,  $I_K/2$ , in the Krummenacher feedback network, can be set by means of a peripheral DAC.  $I_K$  current equal to 25 nA results in a ToT close to 400 ns for an input charge equal to 30000 electrons in high gain

**Figure 14:** Arrangement of front end flavors in RD53A. The pixel column number range of each flavor is shown along the bottom. The digital readout architecture used is also indicated: Central Buffer Architecture (CBA) or Distributed Buffer Architecture (DBA).

Figure 15: Schematic of the Linear analog front end flavor

configuration. The designed sensitivity in the high gain configuration is 15 mV/ke-, and 7.5 mV/ke- in the low gain mode. The core element of the charge sensitive amplifier is the gain stage shown in figure 16. This is a folded cascode architecture including two local feedback networks, composed by the M4-M5 and M7-M8 pairs, boosting the signal resistance seen at the output node. With a current flowing in the input branch equal to 3  $\mu$ A and a current in the cascode branch close to 200 nA, the CSA is responsible for most of the power consumption in the analog front-end. The DC gain and the -3dB cutoff frequency of the open loop response, as obtained from simulations, are 76 dB and 140 kHz respectively. The noise performance of the charge preamplifier is mainly determined by the contributions from the CSA input device and from the PMOS transistor part of the feedback network. The simulated equivalent noise charge, for a detector capacitance of 50 fF,

Figure 16: Linear front end charge sensitive amplifier forward gain stage.

Figure 17: Linear front end threshold discriminator schematic diagram.

is equal to 87 electrons. The front-end channel includes a high-speed, low power threshold discriminator, based on current comparison, connected at the preamplifier output. Shown in figure 17, it includes a transconductance stage whose output current is fed to the input of a transimpedance amplifier providing a low impedance path for fast switching. A couple of inverters is used after the transimpedance amplifier in order to consolidate the logic levels. The performance of the analog front-end in terms of threshold dispersion are greatly improved by the use of a 4 bit, in-pixel binary weighted DAC providing local threshold trimming. From circuit simulations, threshold dispersion before correction is equal to 380 electrons, reduced down to 35 electrons after tuning.

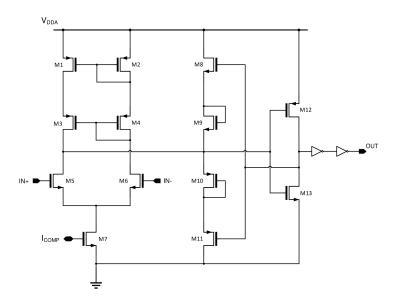

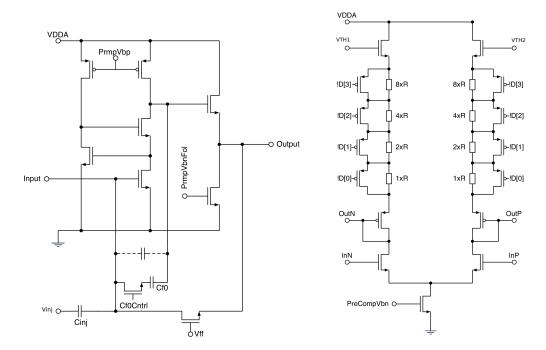

#### 5.2 Differential Front End Design

420

The Differential front end is a pure analog circuit: it contains no memory latches, flip-flops or counters. Static configuration values are provided by the digital core, which receives only the comparator out signal from the analog part. The design is a small-area low-power free-running front-end, for negative input charge. The ADC function is implemented entirely in the digital core, by digitizing the time-over-threshold (ToT) of the comparator pulse. Fig. 18 shows the Diff. FE block diagram.

Figure 18: Schematic of Differential front end flavor.

The pre-amplifier or first stage (Fig. 19) has a simple straight regulated cascode architecture with NMOS input transistor in weak inversion. It has a continuous reset and adjustable gain by choosing between two possible values of feedback capacitance (this choice is made globally, not per pixel). The preamp can operate at very low currents and has three bias currents: the main preamp bias (input transistor current), voltage follower, and continuous feedback current. The feedback current is set globally and cannot be trimmed in each individual pixel. Prototype measurements showed that fall time dispersion (which leads to a ToT dispersion) has an acceptable level without any need for per-pixel trimming. The preamp is single ended, but the feedback ensures that, in the absence of signal, input and output are at the same potential. Input and output are thus taken as a differential input to the next stage.

The DC-coupled pre-comparator or second stage (Fig. 20) provides additional gain in front of the comparator and also acts as a differential threshold circuit. The global threshold is adjustable through two distributed voltages (VTH1 and VTH2) which introduce an offset between the two branches of the pre-comparator. The threshold is trimmed in each pixel using one 4-bit resistor ladder in each pre-comparator branch. The branch current is turned into additional voltage offset by these resistor ladders. An effective 5-bit adjustment is obtained by adjusting one branch resistance

Figure 19: LBNL First stage (preamp) schematic.

**Figure 20:** LBNL Second stage (precomparator) schematic.

or the other using a single 4-bit value. The  $5^{th}$  bit is thus a select bit, which determines which branch is adjusted. The branch that is not adjusted is set to all 1 or all 0, depending on a global configuration value. This design is optimized for low-threshold operation. The pseudo-differential design reduces variation due to mismatch and provides improved power supply rejection. The precomparator stage is followed by a classic continuous time comparator stage with output connected to the digital pixel region through logic gates. Designed for  $500e^-$  threshold operation, the analog pixel has a current consumption of  $4\,\mu\text{A/pixel}$  at  $50\,\text{fF}$  detector load and  $10\,\text{nA}$  leakage current, but can operate up to  $100\,\text{fF}$  load and  $20\,\text{nA}$  leakage, resulting in higher threshold and higher power. It can also meet performance specifications with  $3\,\mu\text{A/pixel}$  current consumption and  $50\,\text{fF}$  load. For leakage currents below  $10\,\text{nA}$ , the continuous feedback is capable of preventing the input from saturating. For leakage of order  $10\,\text{nA}$  or higher, a the leakage current compensation circuit shown in Fig. 18 is required to prevent saturation. This circuit can be globally enabled or disabled. When disabled, the circuit is disconnected from the input, which improves phase margin and noise. It is expected that the Diff. FE will be able to operate without the leakage current compensation circuit for planar sensors even after significant radiation damage.

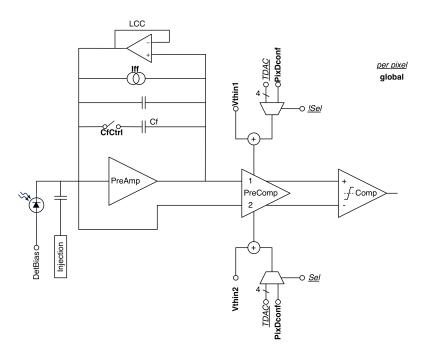

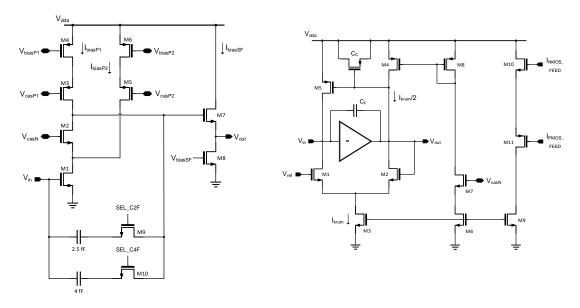

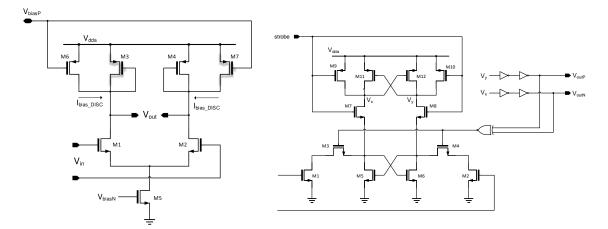

#### 5.3 Synchronous Front End Design

A block diagram of the Synchronous front end is shown in Fig. 21. It features a single stage Charge Sensitive Amplifier (CSA) with a Krummenacher feedback AC coupled to a synchronous discriminator composed of a Differential Amplifier (DA) and a positive feedback latch.

The CSA (Fig. 22) contains a telescopic cascode stage with current splitting to minimize noise contributions and a source follower to improve the driving strength. The Krummenacher feedback

Figure 21: Schematic of the Synchronous front end flavor.

(Fig. 23) is designed to provide both the sensor leakage current compensation and the constant current discharge of the feedback capacitor. The larger the current the faster the preamplifier signal returns to the baseline. As a reference, a 10 nA current results in a 400 ns long signal for an input charge of 10ke-, which is reduced to around 100 ns for a 40 nA current. Two capacitors, equal to 2.5 and 4 fF, respectively, have been included in order to implement different gain values. The calibration injection circuit is described in Sec. 5.4. The preamplifier open loop gain is around 60 dB.

**Figure 22:** Sync. FE Charge Sensitive Amplifier (CSA) schematic. **Figure 23:** Sync. FE Krummenacher feedback schematic.

Due to mismatch effects, considerably relevant in deep submicron technologies like 65nm, the output baseline of the first stage is subject to quite large fluctuations (of the order of tens

**Figure 24:** Sync. FE discriminator schematic.

Figure 25: Sync. FE latch schematic.

of mV) between different channels. In order be immune to such differences an AC coupling to the discriminator (DA) has been implemented. The DA (Fig. 24) provides a further small gain (around 2). However, transistor mismatch results in an offset of the DA output voltage between pixels, that has traditionally been compensated with trim DACs (as for the other front end flavors). Instead, the Sync. FE compensates offsets using internal capacitors to implement an "auto-zeroing" mechanism. This requires acquisition of a baseline every  $100 \,\mu s$  or less. The baseline acquisition takes  $100 \, ns$  and is intended to take place during LHC abort gaps. During collisions, the difference signal (signal minus stored baseline) is fed into the positive feedback latch stage (Fig. 25), which performs the comparison and generates the discriminator output. This stage has been designed to minimize mismatch effects causing a dynamic offset resulting in an additional threshold dispersion. Furthermore, the latch can be turned into a local oscillator up to  $800 \, MHz$  using an asynchronous logic feedback loop, and so used to perform a fast Time-over-Threshold (ToT) counting.

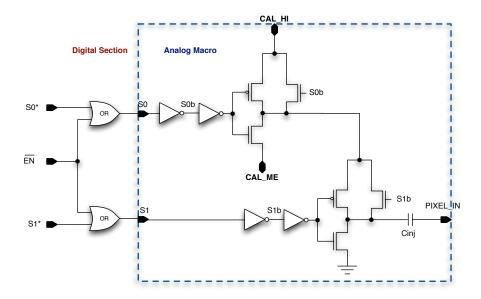

#### 5.4 Calibration Injection Circuit

The calibration injection circuit uses two distributed DC voltages plus in-pixel switches to chop them and generate steps fed to an injection capacitor. Having two voltages allows a precision differential voltage that will be independent of local ground drops in the chip, as well as two consecutive injections into the same pixel. The circuit topology is shown in Fig. 26. Every pixel (regardless of front end flavor) contains the same circuit. The control signals, S0 and S1, are generated in the digital domain as explained in Sec. 5.4.1 and can be phase shifted from bunch crossing clock with a fine delay, which is global for the whole chip. The enable bit is programmable for each pixel. The cascaded "inverter" configuration makes for simple control without the need to synchronize non-overlapping edges. Injection takes place only for cal enabled pixels when either S0 or S1 switch from low to high. Analog injection must therefore be primed by setting at least one control signal low, prior to being able to inject. This priming is not automatic, so that the user is able to control the amount of settling time allowed prior to injection. The CAL command is used for both functions: prime and inject (see Sec. 9.2).

Figure 26: Calibration injection circuit in each pixel.

Just as in a common inverter, there will be a switching transient when a control signal switches from low to high. Simulations show these transients to have a negligible impact on the distributed CAL\_HI and CAL\_MED voltages. Note that at the top of each inverter there is an NMOS transistor in parallel with the PMOS, which switches first (before the PMOS) when injecting. This allows the switches to operate for any choice of voltages CAL HI>CAL MED>GND, but since the top NMOS switches first, it does not contribute transients during injection. During priming, on the other hand, the top NOMS switches first, while the bottom NMOS is still conducting, resulting in a short circuit lasting one inverter delay. This will cause a transient on the CAL\_HI and CAL\_MED voltages, and the user must therefore allow some settling time between priming and injection. In addition to this transient, priming injects a positive polarity pulse into each enabled front end, so one must allow for the front end to settle in any case. The two-voltage injection circuit allows injection of two successive pulses without priming in between, and with arbitrary delay between these pulses. This is a new feature not found in previous chips. The two voltages also mean that the charge injected by S0 is given by a differential voltage and not affected by local ground potential differences. Leaving S1 set and only toggling S0 will result in single pulse differential injection. The two voltage system also makes it possible to inject different amount of charge simultaneously in neighboring pixels by changing the meaning of S0 and S1 in different pixels (see Sec. 5.4.1.

#### 5.4.1 Generation of S0 and S1 signals

The signals S0 and S1 of Sec.5.4 exist locally in each pixel but are derived from different internal signals produced by the command decoder and distributed to the array. This two-step scheme is necessary in order to have either sequential or simultaneous injection, and more importantly to avoid having to distribute two switching signals with precise timing. Since the calibration input is used to study and calibrate timing, it must occur simultaneously in all enabled pixels, just as is the case for the bunch crossing clock (here, simultaneously means within a 2 ns window). Two control

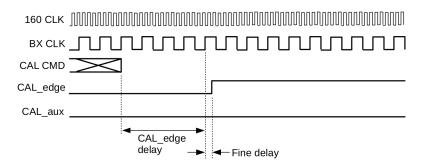

signals are distributed: CAL\_edge and CAL\_aux. As the name implies, CAL\_edge needs to be simultaneous in all pixels, while CAL\_aux does not. CAL\_edge has a fine phase adjustment relative to the beam crossing clock, which is called CAL\_delay. In fact CAL\_edge looks like a traditional injection pulse, with user controlled leading edge time and duration. In *uniform* injection mode (which allows injecting two pulses close in time into all selected pixels), S0 and S1 are derived from CAL\_edge and CAL\_aux identically for all pixels:

$$S0 = CAL\_edge \ OR \ CAL\_aux$$

(5.1)

$$S1 = \overline{CAL\_edge} \ AND \ CAL\_aux \tag{5.2}$$

The rising edge of CAL\_edge throws the S0 switch, while the falling edge throws the S1 switch. The CAL\_aux starts low and then goes high after CAL\_edge, but not with precise timing. In uniform mode the injection switches can only be thrown in that order. Either only use S0 for single pulse, differential voltage injection, of use S0, then S1, for double pulse injection.

In order to allow injection of different size pulses simultaneously into adjacent pixels, there is an *alternating* analog injection mode that can be selected instead of the default uniform mode. In this mode the S0 and S1 signals are derived as above only for *even* pixels, but swapped for *odd* pixels:

$$S1_{odd} = CAL\_edge \ OR \ CAL\_aux$$

(5.3)

$$SO_{odd} = \overline{CAL\_edge} \ AND \ CAL\_aux$$

(5.4)

where an even (odd) pixel is one for which the sum of row + column is an even (odd) number. Thus, for example, in single injection mode the CAL\_edge rising edge throws S0 for even pixels, but S1 for odd pixels. The S0 and S1 assignment options are independent of the cal enable bit in each pixel. The Analog Mode bit of the injection configuration controls whether injection is uniform (mode=0) or alternating (mode=1).

#### 5.5 Analog Bias

520

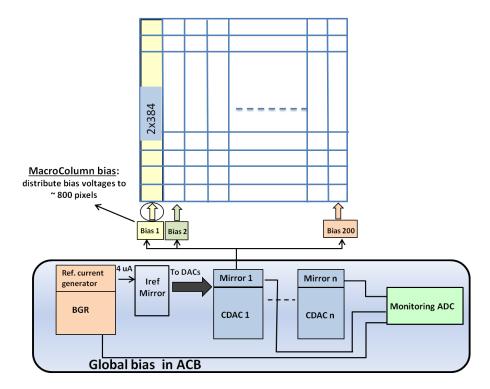

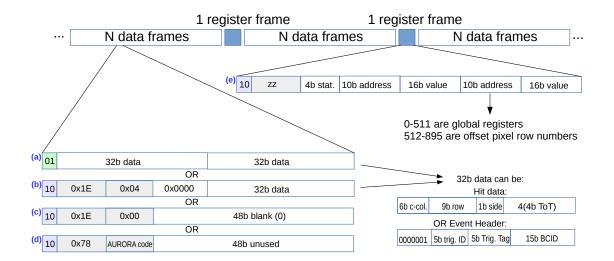

The Front-end bias circuitry is organized in a 2-stage structure, as shown in Fig. 27: the global voltage/currents are globally provided by a set of 10-bit current steering Digital-to-Analog Converters housed in the ACB macroblock. After some current scaling to obtain the requested range and resolution, the biases are distributed to the so-called MacroColumnBias cells, where the final bias/voltage is produce and distributed in parallel to the 384 pixels (768 in the production chip) of two adjacent columns, called Macrocolumn. The MacroColumnBias cell is housed just below the first pixel row and is replicated 200 times. The main advantage of this 2-stage scheme is that a failure in a pixel involving the bias lines will affect only 2 columns, thus improving the overall reliability of the chip. Moreover, the degradation caused by the expected increase of leaking current with radiation is much more limited respect to the scheme where the full matrix is biased in parallel. The main drawback of this concept is the possible increase of bias mismatch among pixels, but since the first stage of current mirroring (between Global Bias and Macrocolumn Bias) can be realized with large transistors, Monte Carlo simulations show that this worsening is negligible. The reference current for the DACs is generated using a Bandgap Reference Voltage circuit and can be finely tuned using a 4-bit DAC to compensate for process variations. The optimal value of this

4-bit DAC will be found during the chip characterization and hard-wired with bonding pads. It's also worthwhile to mention that all the DACs currents can be read back using the 12-bit Monitoring ADC.

Figure 27: Block diagram of front-end bias scheme.

#### 6. Digital Matrix

565

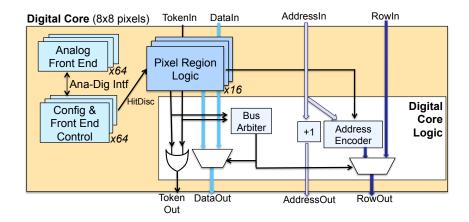

The pixel matrix is built up of digital *cores* with 8 by 8 pixel channels each, contained in 4 by 4 analog islands. The core is synthesized as one digital circuit. It provides static configuration bits to the analog islands, and receives four binary outputs from each island. The digital core handles all processing of the binary outputs, including masking, digital injection, ToT counting, storage of ToT values, latency timing, triggering and readout.

Each core receives all input signal from the previous core closer to the chip bottom, and regenerates the signals for the next core. The timing critical clock and injection edge signals are internally delayed within the core relative to the regenerated ones so that when all the cores are integrated there is uniform timing (within 2 ns) of those signals within all cores. To achieve this uniformity there are multiple core delay values used in RD53A, with the largest (smallest) delay used in the top (bottom) third of the matrix. Other than this delay value, all cores of the same flavor are identical. The bunch crossing clock and calibration injection signals can be separately gated off to individual columns of cores.

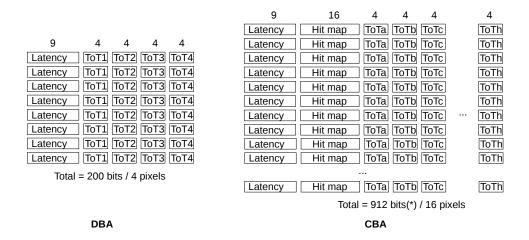

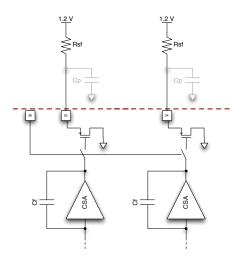

**Figure 28:** Diagram of memory maps for DBA (left) and CBA (right) regions.(\*)The number of ToT storage locations per latency timer for the CBA has been maximized to fill the available layout space and does not reflect the minimum number needed for physics.

There are two core flavors implementing two readout architectures, called DBA (Distributed Buffer Architecture) and CBA (Central Buffer Architecture) covering the column ranges indicated in Fig. 14. In both cases the basic unit is called a *region*, which can be thought of as a macropixel with internal structure. The DBA (CBA) region size is 4 (16) pixels. In both cases, timing information (when a hit occurred) is stored by region, not by pixel. In the DBA region ToT information is stored by pixel, while in the CBA region there is a common region memory where ToT information is stored. In this way, the CBA suppresses zero ToT values, but at the cost of having to store a hit map, while the DBA "wastes" memory storing zero ToT values, but needs no hit map. The DBA is efficient as long as multiple pixels are typically hit (high region occupancy- few zero ToT values), which is the case for a small region. The CBA architecture is efficient as long as region occupancy

is low (most pixels hit is very rare), which is the case for larger regions. The memory usage of both architectures is illustrated in Fig. 28, which is further explained if Sections 6.1 and 6.2. The total storage in the DBA region is 50 bits per pixel, while the RD53A CBA region has 57 bits per pixel, because the amount of ToT storage has been maximized to fill available space. The different architectures have a negligible impact on the digital chip bottom design, because the output data formats have been kept identical. The advantage of one of another in terms of region layout area and resources depends on the size of the latency timers and the ToT registers. For 9 bit timers and 4 bit ToT they are similar. A 2 bit ToT would clearly favor DBA, while a 6 bit ToT would clearly favor CBA.

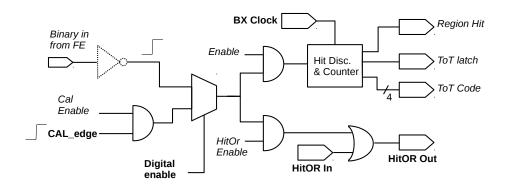

**Figure 29:** Digital processing chain for a single binary output from an analog island. The bold text indicates global signals, while the italic text indicates local pixel signals. The CAL\_edge signal is the digital injection pulse input. The dotted line inverter is only present for the Diff. FE.

#### **6.1** Distributed Buffer Architecture (DBA)

Each core is logically divided into 16 4-pixel regions, which have identical functionality, but differ in address and are not identical in terms of layout because they are all synthesized together in one flat layout (dubbed digital sea). Each region spans 4 columns and one row and therefore covers an effective area of  $50\,\mu\text{m} \times 200\,\mu\text{m}$ . In terms of a sensor this means  $1\times4$  50x50 pixels or  $2\times2$  25x100 pixels. Because the beam spot is extended in Z, clusters in the detector barrel have a rectangular rather than square shape and are more efficiently recorded with  $50\,\mu\text{m} \times 200\,\mu\text{m}$  regions than they would be with  $100\,\mu\text{m} \times 100\,\mu\text{m}$  regions. Note that there is no one-to-one correspondence between 4-pixel analog islands and 4-pixel digital regions.

Each individual pixel output is processed as shown in Fig. 29 The pixel output feeds two data paths: the triggered DAQ path (Sec. ??), and the prompt path, also called Hit OR, where a hard-wired OR of many pixel outputs is made available in real time to output pads and/or bottom of chip processing. These outputs can be independently masked for each pixel, via the Enable and HitOR pixel configuration bits (see Sec. 6.3).

The Hit Discriminator and Counter block in Fig. 29 is responsible for determining if an intime hit is present and what is the ToT value to be stored. The block does *not* contain a method to separate "small hits" from "large hits" as in the FE-I4 chip. All hits fire the region hit output,

#### PixelRegionLogic PixelLogic PixelLogic PixelLogic PixelLogic BX cloc Read Mem ↓ Addr region hit region hit ▼ region hit region hit Data Data Timestamp count np mem Timestamp + Lat Trigger match Trigger Trigger Id Trigger Id check Trigger Id Req Arbitration Token In Pixel Region Data (4 4-bit ToT) Token Out

Figure 30: 4-Pixel region with 8 shared latency timers and 8 ToT memories (4 bits each) per pixel.

Figure 31: Block diagram of digital core with multiple regions.

which in turn starts a latency counter for the whole pixel region. If multiple pixels fire in the same region in the same crossing, still only one latency timer starts. ToT is counted independently for each pixel using the 40 MHz clock. If the counter reaches maximum while the pixel comparator output is still high the counting concludes and the maximum ToT is recorded (Any ToT value 15 or greater is encoded as ToT code 0xF).

605

Each 4-pixel region has 8 latency timers and each pixel has 8 ToT storage registers, 4 bits each (Figs. 28, 30). The latency timers are common to the whole region, but the ToT storage is at the single pixel level- hence the name Distributed Buffer Architecture. Each of the 8 ToT registers is associated with one latency timer (hard-wired). This way when one pixel is counting ToT it does not prevent the other pixels in the region from being hit: no region dead time.

The latency timers are 9 bits wide, allowing for a programmed latency of up to 511 bunch crossings. The timers are idle until a hit arrives and with each new region hit (the OR of all 4 pixel hits) a new timer is started. Only one timer can start in any given bunch crossing regardless of how many pixels were hit. When a timer reaches the programmed latency and no trigger is present, it is

reset and the associated ToT values erased. If a trigger is present, then the ToT values are not erased and a trigger tag is stored to label the hits for later readout. Readout proceeds with column-parallel token chain, one trigger tag at-a-time. The organization of a core is shown in Fig. 31.

#### **6.2** Central Buffer Architecture (CBA)

635

A CBA region is 4 by 4 pixels. It contains region latency timers as described in Sec. ??, but it has 16 instead of 8, since more hits can occur in the larger region. The difference is in the ToT storage, which uses one shared buffer rather than individual buffers for each pixel. Since each latency timer serves 16 pixels, larger clusters can be stored more efficiently and fewer clusters will straddle a region boundary. Instead of storing the full ToT for each pixel, a region hit map (16 bits) is also stored with each timer. Then the 4-bit ToT value for up to 8 hits is stored in a shared buffer (see Fig. 28). A fixed priority queue is used to uniquely assign each stored ToT to a given hit pixel. If more than 8 pixels are hit (which is very unlikely) the ToT information for the additional pixels is lost, but the full hit map is always preserved. A diagram of the CBA organization is shown in Fig. 32.

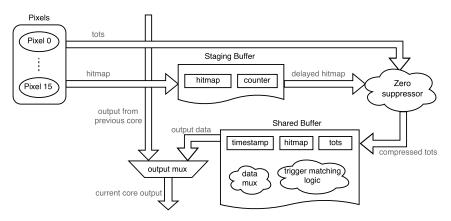

The ToT zero suppression requires the ToT digitization to be be completed. While in CHIPIX this was achieved by using fixed dead-time counters in the pixels, in RD53A, an intermediate "Staging Buffer" has been added. The Staging Buffer saves a copy of the hit map and holds it until all pixels have completed ToT. A new hit arriving in the region during this time can be accepted and will create a new hit map. The Staging Buffer can host up to 4 events: if there are more than 4 hits in a period of time equal to the Write Synchronization Time, there is a hit loss.

Figure 32: Block diagram of Central Buffer Architecture region logic.

Every pixel generates a "Hit Present" pulse when the output of the discriminator is high. A region-wide OR of these signals is used to trigger the Staging Buffer. All the Hit Presents are written in a row to create the hit map and a counter is started. When the counter reaches the Write Synchronization Time (configurable), it feeds the hit map to the ToT zero suppression stage. The Write Synchronization Time should therefore be fixed at the maximum expected number of 40MHz clocks required to compute the ToT in the pixels. Given that CBA features the SYNC FE, the minimum value of this configuration register depends on the frequency of the Fast clock for fast ToT computation. The hit map and the 8 zero suppressed ToT values are only written to the shared buffer of Fig. 28 once the Write Synchronization Time has elapsed.

The trigger logic that selects hits for readout is the same as for the DBA. A dedicated adapter stage along side the column read control at the chip periphery constructs DBA-like output packets and feeds them to the data concentrated in the digital chip bottom. This makes the data identical for both region architectures. The only difference in the DBA and CBA output data is in the meaning of ToT code 0xE. In CBA data this code is not a ToT value 14, but rather a flag indicating that some ToT were lost due to zero suppression. Any ToT value 14 or greater is encoded as ToT code 0xF.

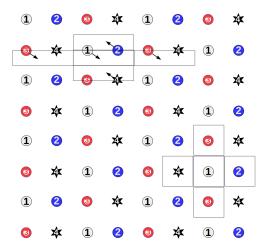

#### 6.3 Hit OR

In RD53A there are actually four independent Hit OR networks, each one fed by one quarter of the pixels. Fig. 33 shows graphically how the 64 pixels in one core are grouped into the 4 OR networks. The figure also indicates two possible sensor formats of  $50\,\mu\text{m} \times 50\,\mu\text{m}$  (50x50) or  $25\,\mu\text{m} \times 100\,\mu\text{m}$  (25x100) pixels. It can be seen that in the 50x50 case, a given pixel in network 1 has its two up-down neighbors on network 3, and its left-right neighbors on 2 and 4. Conversely, a given 25x100 pixel on network has has its left-right neighbors in network 3 and its up-down neighbors on 2 and 4.

**Figure 33:** The four Hit Or networks in a 64 pixel core.

**Figure 34:** Block diagram of digital bottom of chip showing the command input and data output paths

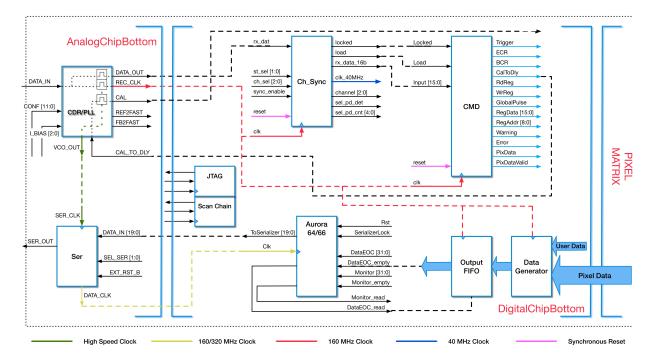

### 7. Digital Bottom of Chip and Clocks

The Digital Chip Bottom (DCB) contains the blocks that implement all control and processing functionality. The entire digital bottom is high level description code synthesized together during top level integration. This includes SEU tolerant configuration memory, which uses a special synthesis flow described in Se. B. However, it is driven by clocks generated in custom layout blocks that are part of the Analog Chip Bottom (ACB), but nevertheless described in this section. Fig. 34 shows the relationship between the various blocks. The programming and I/O protocol details are given in Sec. 9, while chip start up and reset considerations are included in this section.

To provide failsafe functionality and to allow for special tests (such as response to clock jitter), the standard control path of RD53A can be fully bypassed. All bypass functions are controlled from wire bond pads, so there is no possibility they are accidentally enabled or disabled. The chip can be entirely operated without the serial input and clock and data recovery, or one can bypass individual elements in almost any combination.

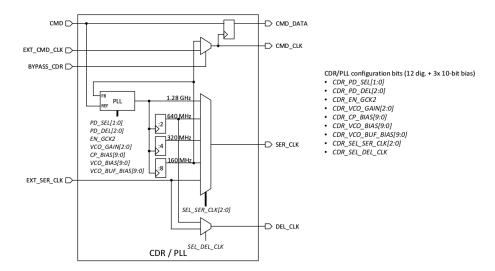

#### 7.1 Clocks and CDR/PLL

660

665

RD53A needs four clocks, most easily identified by their nominal frequencies. Three of them are normally generated by the Clock and Data Recovery (CDR) block (Fig. 35): the 160 MHz clock (CMD\_CLK), the 1.28 GHz clock (SER\_CLK) and the 640 MHz fine delay clock. If the CDR is bypassed by wire bonding the Bypass\_CDR pin to VDD, the 160 MHz must be supplied externally, and will be used to generate the 1.28 GHz and the 640 MHz clocks. The 1.28 GHz clock can also be supplied externally independently of the Bypass\_CDR state, and in this case this externally

Figure 35: Diagram of the CDR (Clock and Data Recovery) block operation options

supplied clock will also be used as the fine delay clock. Selection an external clock source is done by a configuration register. These three clocks do not need to be synchronous nor have any particular ratio between their frequencies. Of course, when they are internally generated they will all be derived from a primary 1.28 GHz clock as shown in Fig. 35.

The CDR is is a custom analog block with an internal Voltage Controlled Oscillator (VCO) and a Phase Locked Loop (PLL) to lock to the incoming 160 Mbps control serial stream. The VCO produces primary 1.28 GHz clock locked to the phase of the command input stream transitions. This primary clock is divided down to produce the needed outputs. In the absence of a control input the CDR will still generate clocks with some frequency of order the nominal values, but arbitrary.

The 40 MHz clock (BX\_CLK), is derived from the 160 MHz clock by the Channel Synchronizer (CS) block and it is the only clock distributed to the pixel matrix (Fig. 34). when dividing the 160 MHz one can choose 4 possible phase shifts for the 40 MHz clock. The CS picks the correct

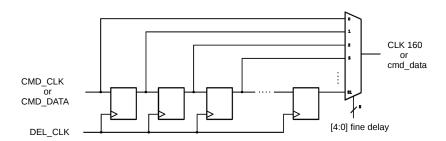

**Figure 36:** Schematic of clock and command phase adjustment, which permits synchronizing every chip's internal clock to the LHC bunch crossings. There is a selectable 2 inverter delay of DEL\_CLK (not shown).

phase using Sync symbols in the command stream as explained in Sec. 9.2. However, before commands are sent to the chip, or if the command stream is interrupted, the the CS must still produce a 40 MHz clock to send to the pixel matrix, as this clock must never stop for proper startup and operation of the matrix. Therefore, upon start up, the CS produces a 40 MHz clock with arbitrary phase and later on switches to the correct phase without ever stopping.

In operation, the 40 MHz BX\_CLK must be synchronized with the accelerator bunch crossings. For this purpose there is a programmable phase delay that can shift the BX\_CLK phase in nominally 1.6 ns steps. This delay is not applied directly to the 40 MHz, but rather to both the 160 MHz clock and the serial command stream, as shown in Fig. 36. Thus it has the same effect as adding a cable delay to the clock/command serial stream. To guard against the possibility of a race condition there is a 2-inverter delay (2INV) that can be selected via configuration for the phase shifter clock.

#### 7.2 Start Up and Reset

Upon start up several actions an initializations must be performed. Some are carried out automatically by a Power On Reset (POR) while others use set/reset commands. For commands to work the chip input path must first initialize and lock, which happens automatically with a supplied input command serial stream, or this default control path must be bypassed as explained in Sec. 7.3. The clock and data recovery lock signal is available on the STATUS output wire bond pad (Table 22): this can be monitored for debugging purposes or could for example drive an LED on a test board. Different parts of the chip follow different reset procedures. Most of the chip logic is in the data path, both within the pixel matrix and in the digital bottom of chip. All this logic is reset with a command called ECR (see Sec. 9.2). There is a dedicated reset for the JTAG interface, which remains in reset if not used, driven by the DEBUG\_EN wire bond pad (Table 22).

**Figure 37:** Power-on reset schematic. Capacitor C1 must be loaded externally with a nominal value of 5 nF. The POR signal, which is active low, is labeled RESET.

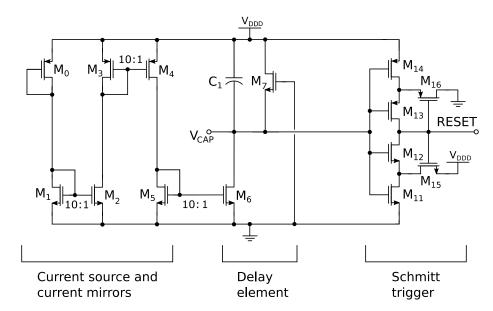

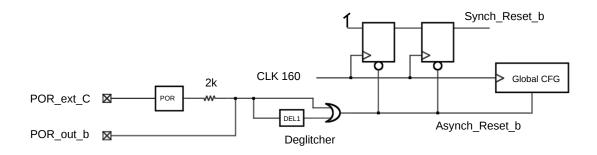

RD53A contains an active low POR generator (low is reset, high is not reset). The main function of the POR is to ensure that the chip has a reasonable configuration immediately after startup and stored logic states are well defined. The POR schematic is shown in Fig. 37. This circuit is itself powered from the digital power internal rail, which is the output, not the input, of the digital voltage regulator. The voltage regulators themselves do not have a reset: they are purely analog circuits. The POR begins with the reset condition asserted (POR output low). A Schmitt trigger fires when VDD exceeds 0.6 V, and 10 ms later the reset condition is removed (POR output goes high). The 10 ms delay assumes a 5 nF value external capacitor to VDDD has been loaded. The delay is linear with the capacitor value. When power is applied it should ramped up faster than this delay. There is no brown-out detection feature in RD53A. The POR output is available on a wire bond pad (Table 14) and can be forced externally if necessary, as shown in Fig. 38. An internal resistor is used to ensure a high output impedance of the POR circuit so that it can be safely forced form the bonding pad if needed.

Figure 38: Power-on reset usage. Nets EXT\_POR\_CAP and POR\_OUT\_B are a available on dedicated wire bond pads.

The POR output is an asynchronous signal that directly controls the configuration memory reset. This reset loads the pre-defined default values in all registers. The pixel configuration registers are not reset. The pixel configuration registers do not have a reset function. Instead, the pixels are switched to use hard-wired default configuration instead of the values stored in their registers. The MUX switch that selects which configuration the pixels use is controlled by one of the global configuration registers (PIXDEF). Thus, there is only one global configuration, stored in registers, which resets to a default value after power up, but there are two pixel configurations, one hard-wired and one stored in registers, and a MUX to toggle between them.

In order to generate a synchronous reset to reset logic circuits, the asynchronous POR output is synchronized with the 160 MHz clock (CMD\_CLK) as shown in Fig. 38. For this to work, the 160 MHz clock must be present before the POR reset condition has been lifted. The CDR circuit (Fig. 35) will in fact generate a clock as soon as it is powered, even if there is no external serial bitstream provided for the PLL to lock to. The frequency of this prompt clock is the Voltage 740 Controlled Oscillator (VCO) frequency divided by 8. While in reset, the PLL is not yet active and the VCO is controlled by the voltage on wire bond pad PLL V VCO (Table 19). As PLL V VCO

735

is internally pulled up to VDDD, if this pad is not connected the VCO will come up at its maximum frequency, which is about 2.5 GHz before irradiation, and this will lead to about 320 MHz logic clock instead of the desired 160 MHz. While this should still be adequate to reset the logic, an external resistor to ground on PLL\_V\_VCO is recommended (value to be determined by test) in order to lower the VCO reset voltage.

On the other hand, if the CDR is bypassed, requiring the user to supply the 160 MHz clock, this external 160 MHz clock should be supplied *before* power is applied for the synchronous reset to work properly.

The synchronous reset acts on the Channel Synchronizer and the Command Decoder blocks (Fig. 34). Immediately after this reset, the Channel Synchronizer will lock to the correct phase of the incoming command stream, using Sync symbols (see Sec. 9.2) and the Command Decoder will begin processing commands. The lock signal will be asserted on wire bond pad STATUS, as mentioned earlier. The user must send an ECR command to the chip in order to reset the pixel matrix and the data path. An ECR is *not* generated automatically by the POR.

# 7.3 JTAG and Command Bypass

750

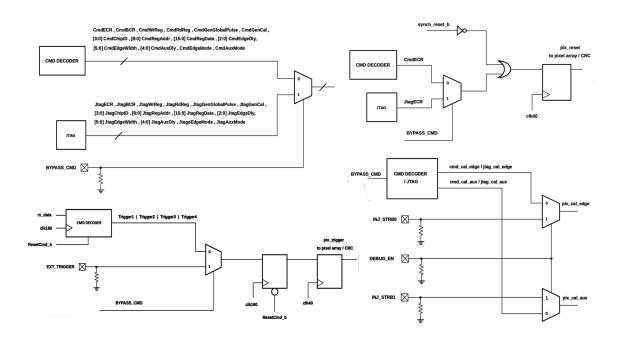

**Figure 39:** Schematic of command decoder bypass options.

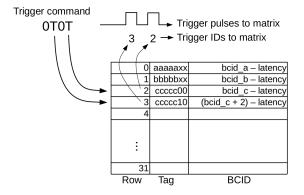

The JTAG interface has a dedicated reset pin as defined in the JTAG standard. This pin has an internal resistor ensuring the default value is in reset, which means the JTAG interface is not used. To use the JTAG interface, this pin must be externally forced, which will take the JTAG out of reset. The JTAG interface can be used to spy on on internal registers even during normal operation and to run structural tests (scan chains). One can also fully control the chip from the JTAG interface and for this the normal command path must be bypassed. Fig. 39 shows how the command decoder