Log

######################################################################################################## 抱えている問題点

-

configが通らない: チップにdirect modeの動作電圧(VDDD=1.3V , VDDA=1.3V)がかかるようにLVを調整すると通るようになった -

direct modeにおいてTEXIOで両方1.3Vかけてもチップに正常な電圧が流れない(だいぶ低くなる): 4pin connectorの接触抵抗?→connectorをKEKで使っているものに付け替え→改善 - LDO modeでconfigが通らない : 電源の立ち上がり?、電圧不足?、LDOが壊れてる?

- std threshold scanが途中で落ちる : メモリーリーク?

- tune thresholdのあとにthreshold scanを行うと落ちる : メモリーリーク?

そもそもconfigが通らない問題

- source /opt/Xilinx/Vivado/2016.4/settings64.shをして、vivadoでVivadoを起動

- Open Hardware Manegerに入り、Open targetのAuto connectをクリック

- xcf7k325t_1を右クリックし、Program Deviceをする

- ~/work/FNALTestbeam2018/XpressK7_RD53A/YARR-FW/syn/xpressk7/bram_rd53a_quad_lbnl-325内のrd53a_quad_lbnl_passive_325_160Mbps_pixregro.bitを焼いてPCをreboot

- src内で"./bin/test"を実行して正常に動くかを確認

LDO modeでconfigが通らない問題

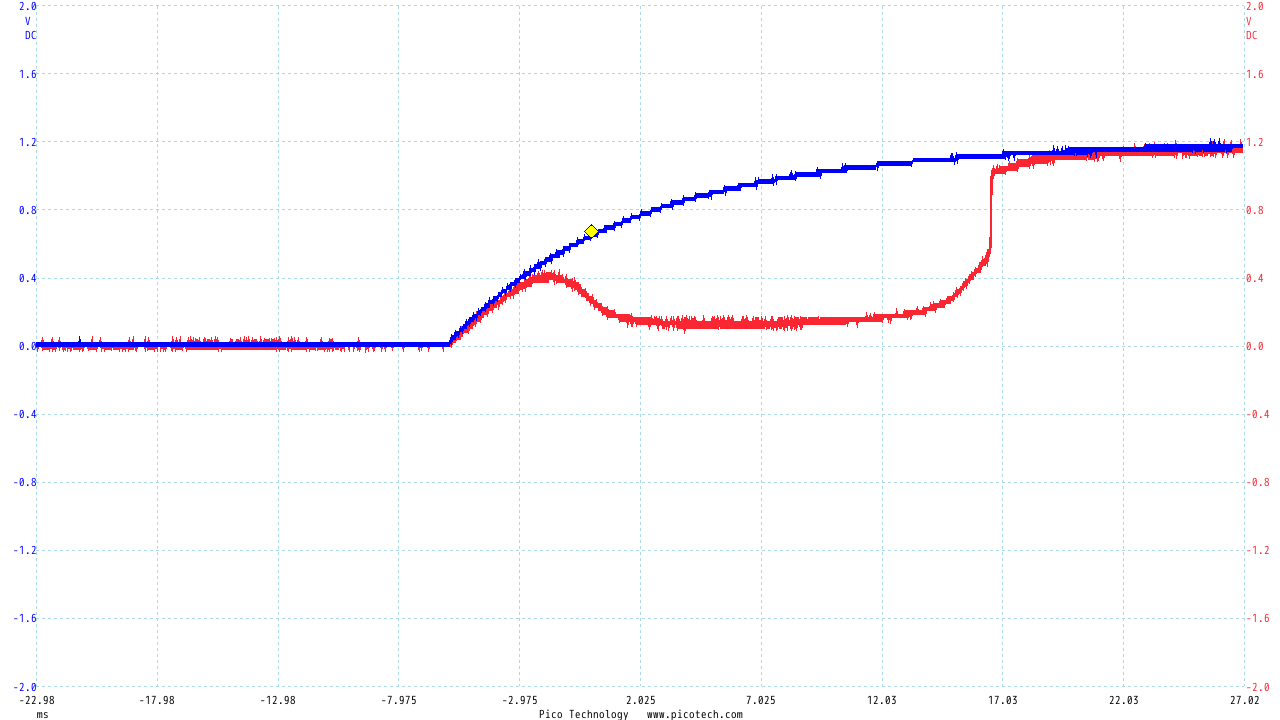

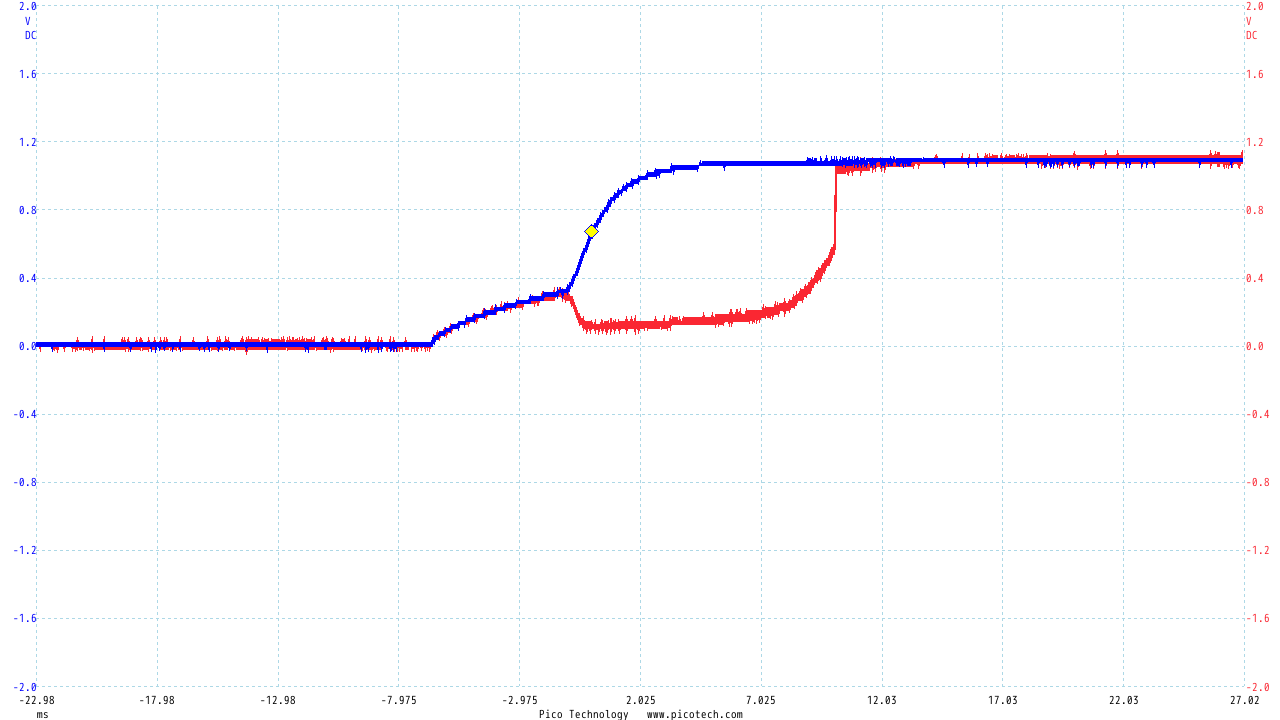

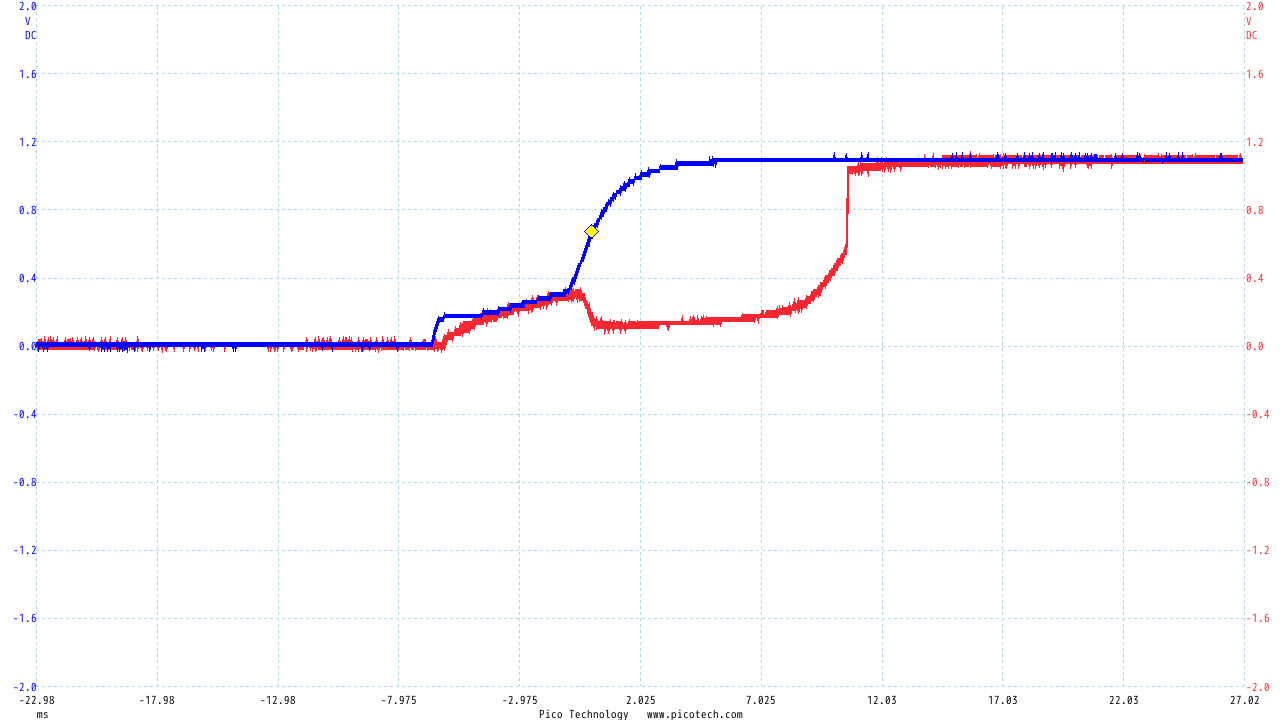

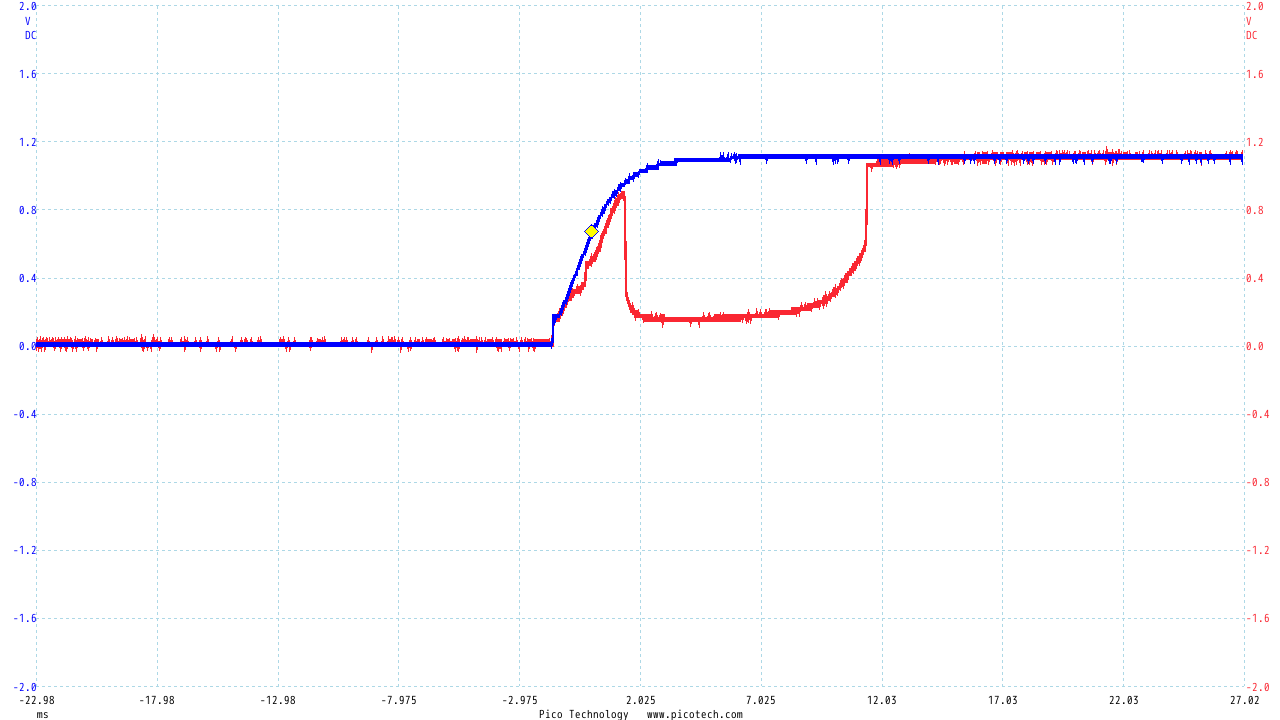

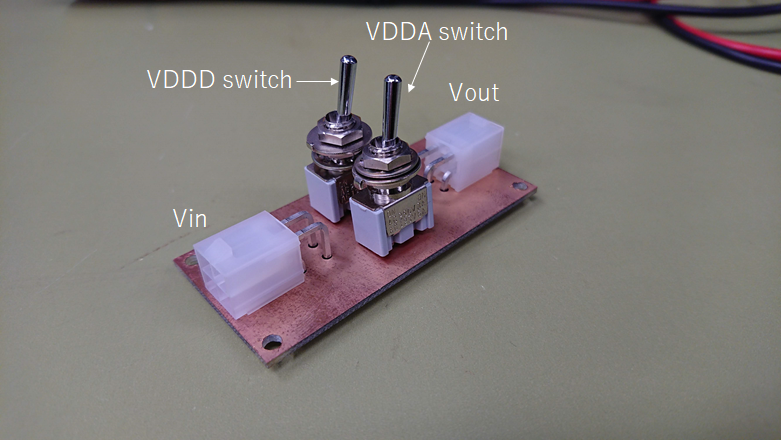

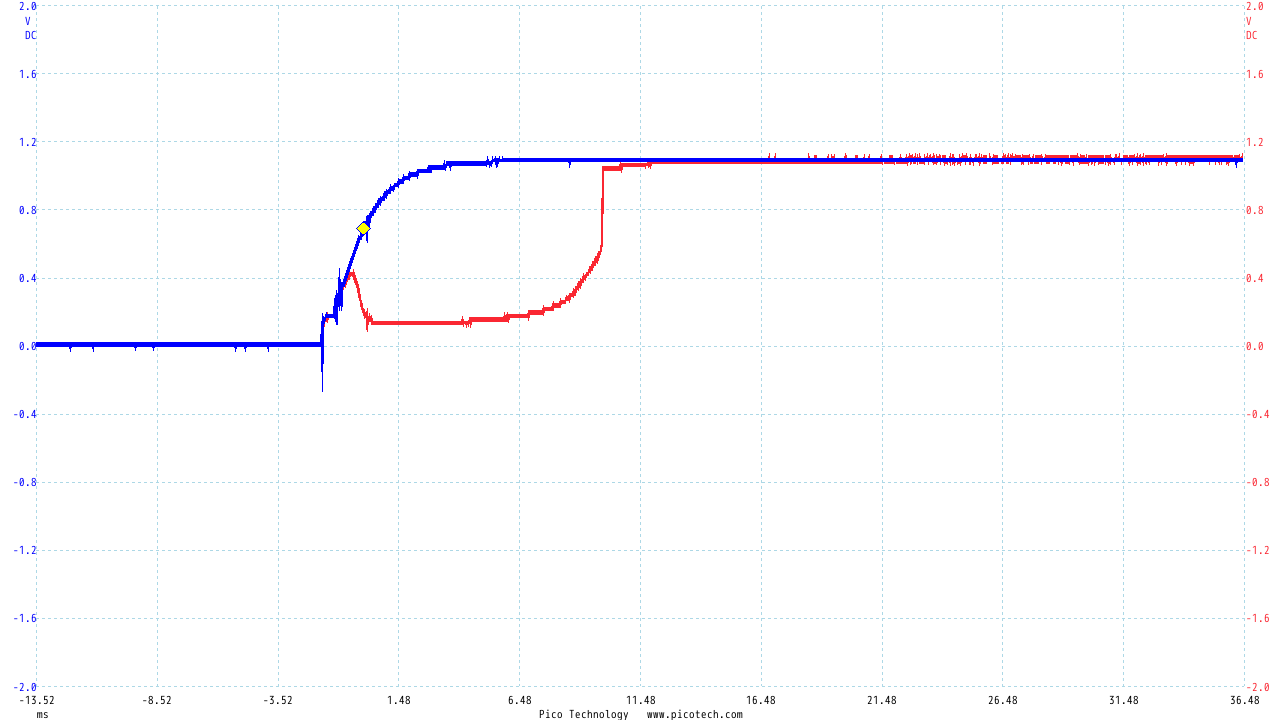

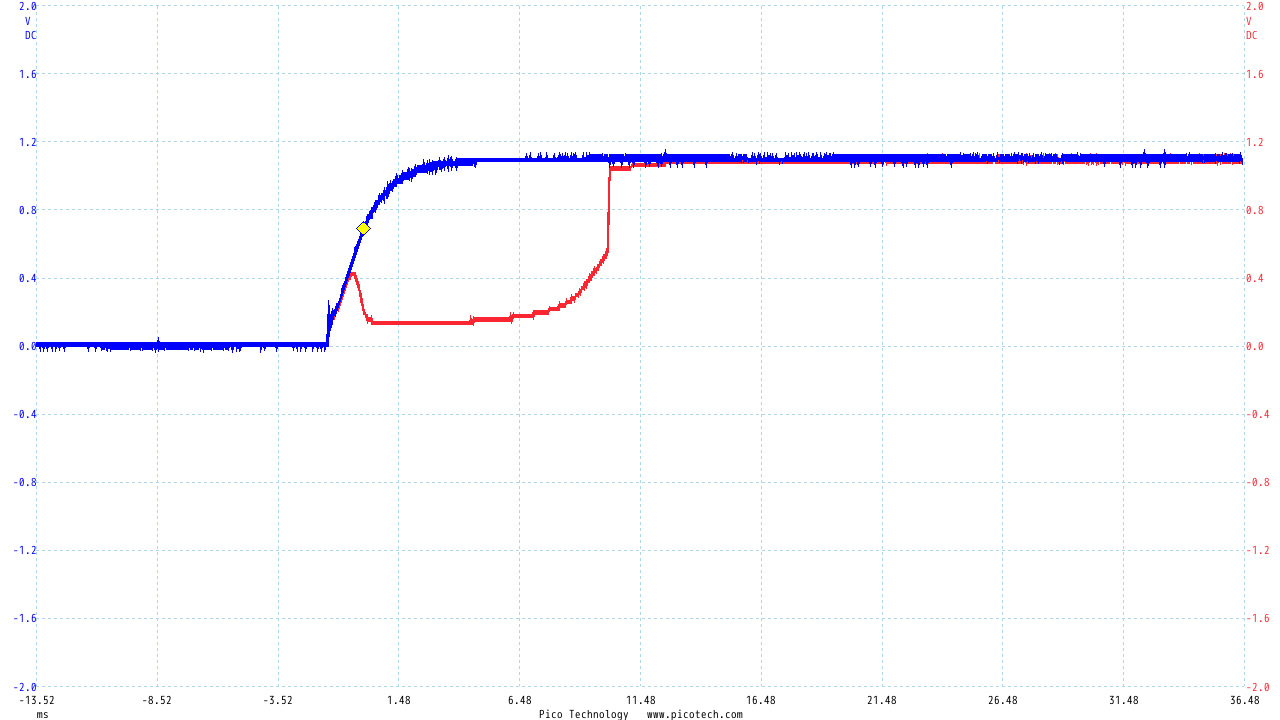

Vin:1.8Vをかけてもconfigが通らない、そもそも何も返ってこない SCCの表面実装をrecommendationに対応させた→ Single Chip Card への変更点→それでもconfig通らず 電源の立ち上がりが安定する前にPORが立ち上がるとconfigが通らないため、PORが働くまでのdelayをpico太郎で見てみる TEXIOだとやはり電源の立ち上がりが遅い?(ただ立ち上がりの遅いdirect modeだとconfigが通る)→立ち上がりの早いUSBpixのregulatorを使ってみる| mode | power | Vout | Waveform |

|---|---|---|---|

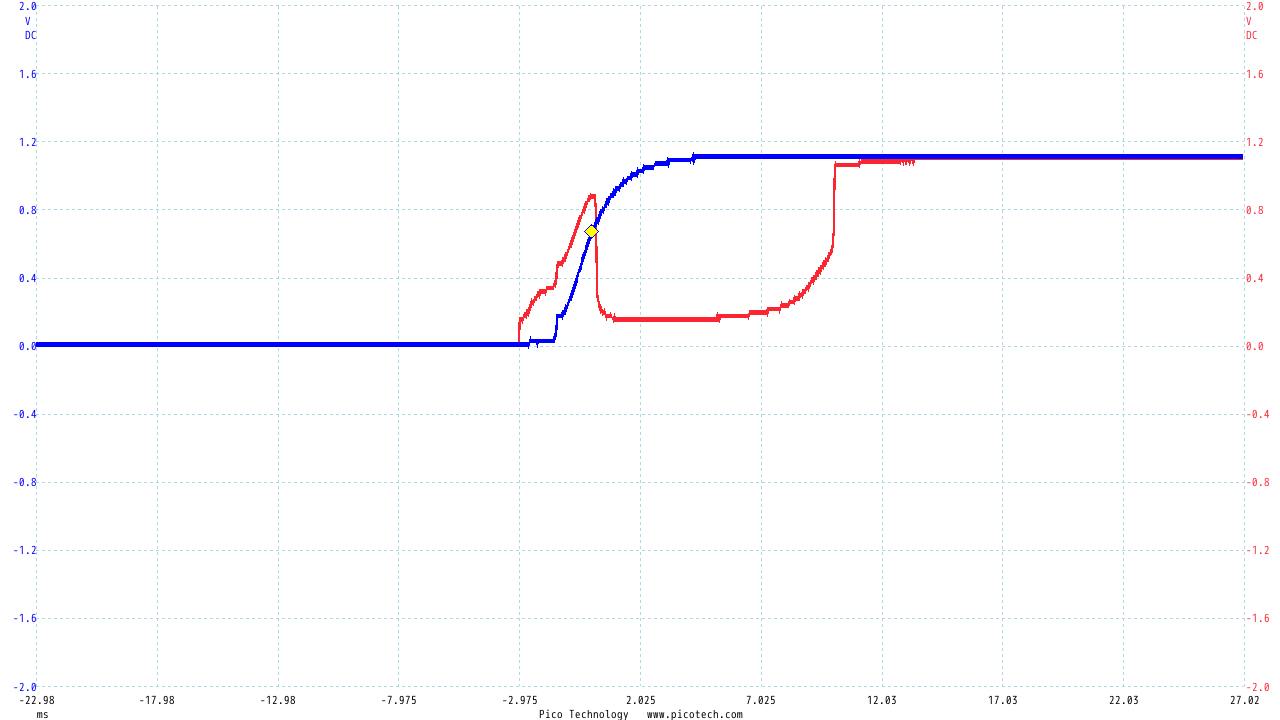

| direct | TEXIO | VDDA |  |

| LDO | TEXIO | VDDA |  |

| VDDD |  |

||

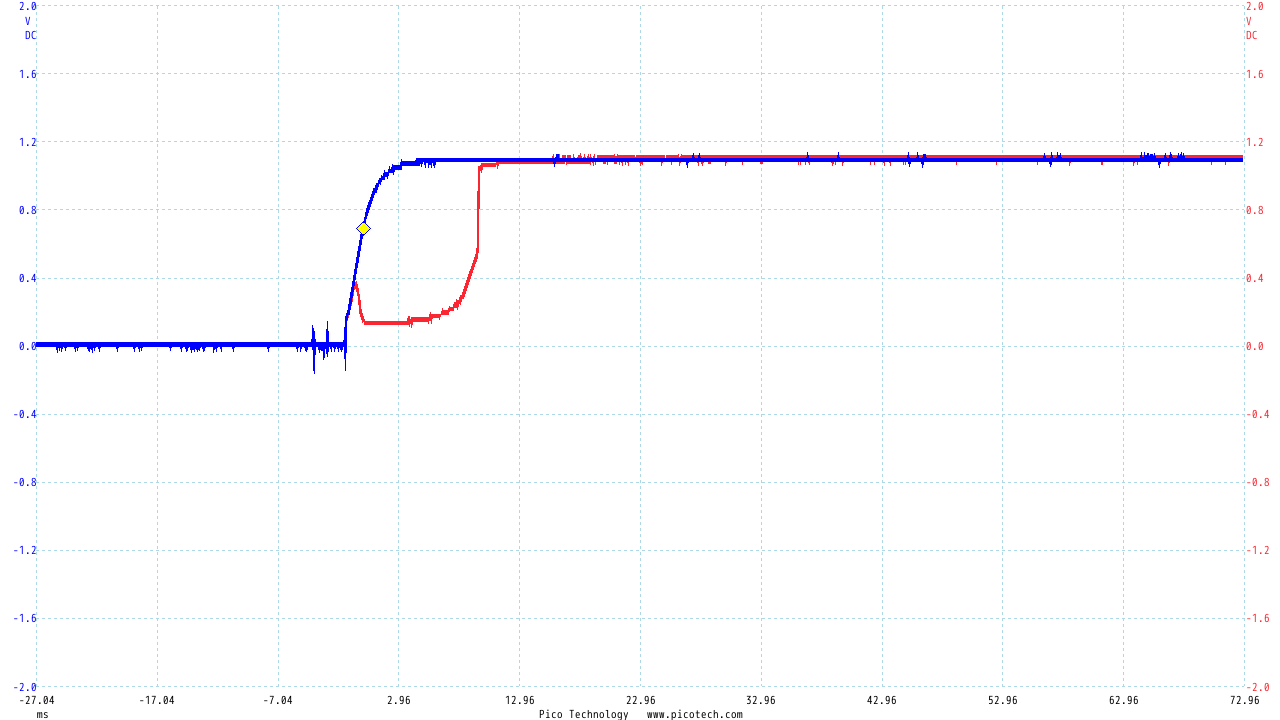

| USBpix | VDDA |  |

|

| VDDD |  |

| mode | power | Vout | Waveform |

|---|---|---|---|

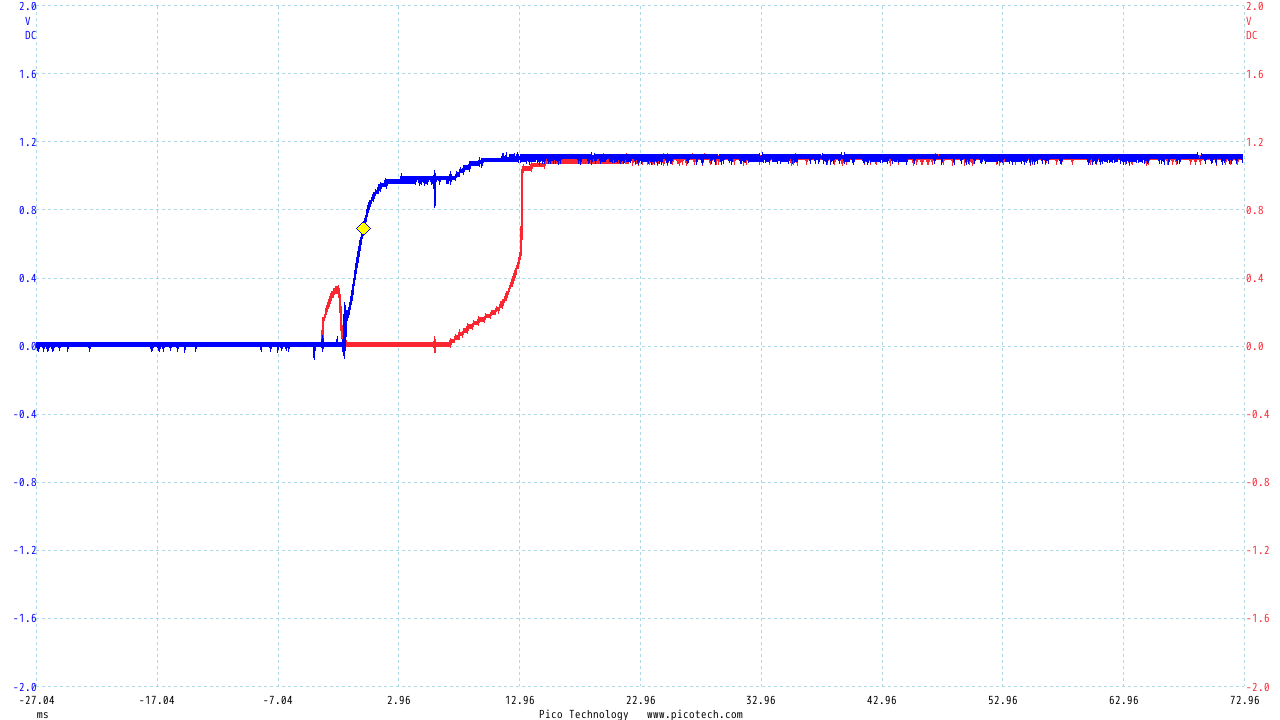

| LDO | switch | VDDA |  |

| VDDD |  |

| mode | power | Vout | Waveform |

|---|---|---|---|

| LDO | switch | VDDA |  |

| VDDD |  |

threshold scan問題

std threshold scanがtune前後関係なく落ちる lin/diff threshold scanに関してはtune後(tuneはlin/diff問わず)に落ちるようになる topを見ながら走らせるとメモリーを使い果たしたことでjob自体がkillされている→メモリーリークかdigital scan問題

direct mode、それぞれVDDD=1.23V,VDDA=1.20Vをかけた状態でdigital scanを行ってもうまく返ってこない dig/anaの電流値を見る限りconfigが通っていそう rd53a_testを走らせると、最初良さそうな結果が返ってくるが、ノイズが以前よりも大分多くなってしまっている --Comments

Topic revision: r4 - 2018-06-08 - AtlasjSilicon

Ideas, requests, problems regarding TWiki? Send feedback